Home appliances 32-bit 3-in-1 MCU

# 1 BF7807AMXX MCU general description

#### 1.1. Features

- > Core: ARM Cortex-M0+

- Operating frequency: 48MHz, 32MHz, 24MHz, 12MHz

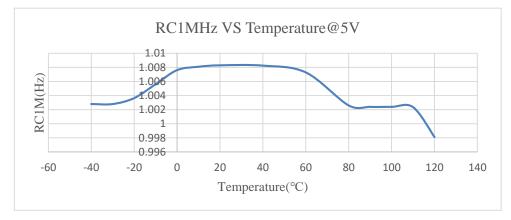

- Clock error: ±1% @-20°C~65°C, 5V

- ±3% @-40°C~105°C, 5V

- > Memory (FLASH)

- FLASH: 128K Bytes, support erase and write protection and read protection functions

- DATA: 512 Bytes

- SRAM: 16K Bytes

- > Clock source, reset and power management

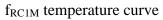

- Internal low-speed RC oscillator: LIRC 32kHz, clock error is ±10% @25°C, 5V, ±25% @-40°C ~105°C, 5V

- Internal high-speed RC oscillator: RC 1MHz

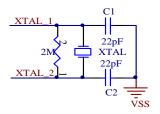

- External crystal oscillator: XTAL 32768Hz/4MHz/8MHz

- 8 kinds of resets, including power-down reset voltage (BOR): 2.8V/3.3V/3.7V/4.2V

- Low voltage detection:

2.7V/3.0V/3.3V/3.6V/3.8V/4.0V/4.2V/4.4V

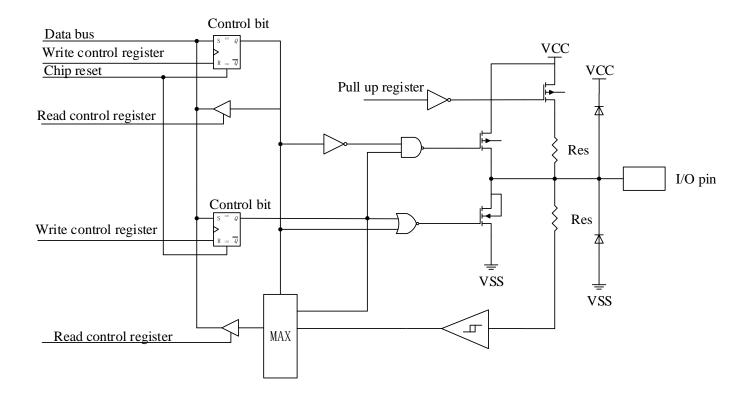

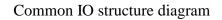

- > 10

- Both support built-in pull-up resistor 33k

- High current sink port (PA0~PA7)

- Support IO function remapping

- Both support external interrupt function (rising edge, falling edge, double edge)

- Communication module

- 5xUART communication module, support IO mapping

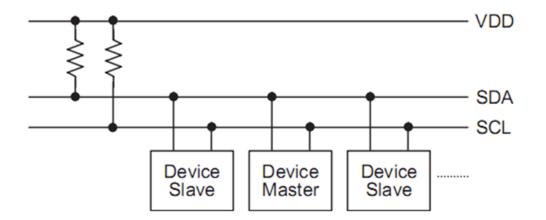

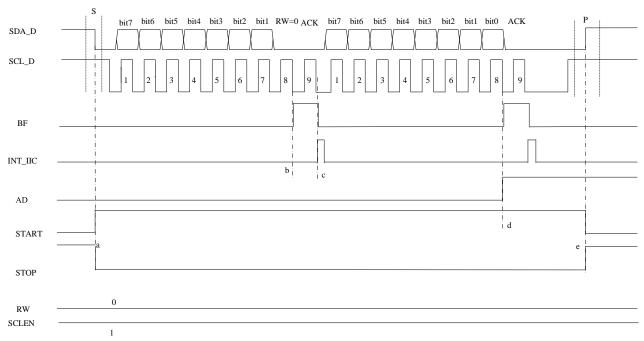

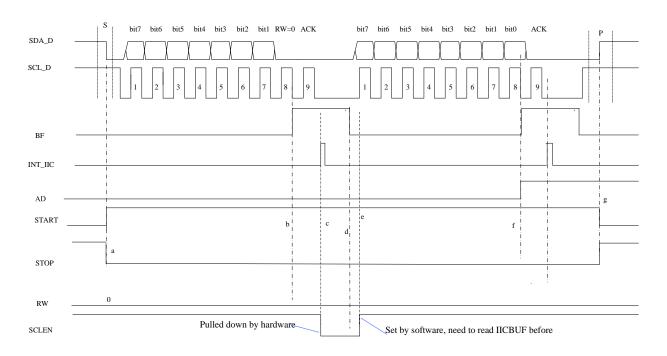

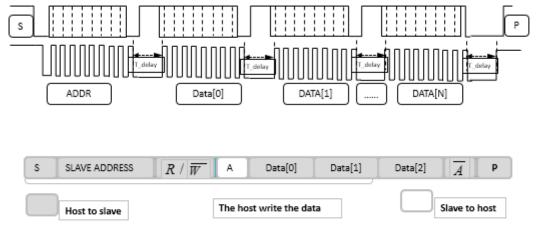

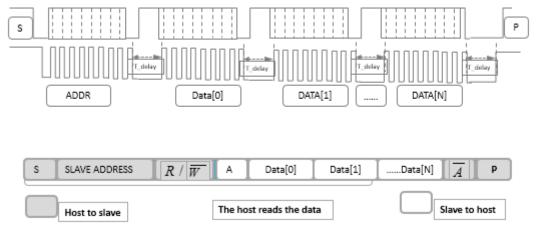

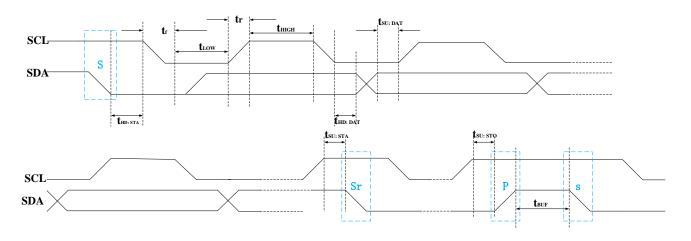

- 1xIIC master-slave communication, both master and slave support 100kHz/400kHz/1MHz

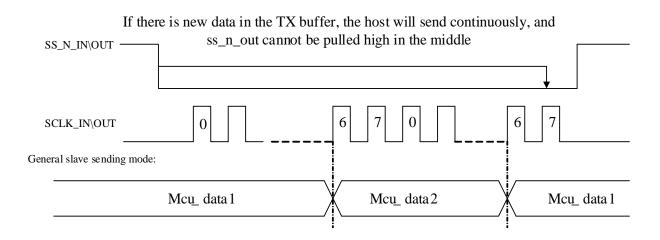

- 2xSPI master-slave communication, the master supports up to 8MHz, the slave supports up to 4MHz

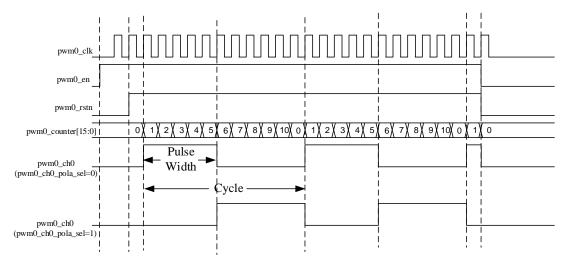

- > 16-Bit PWM

- PWM0/1 both support 5 channels, sharing period, duty cycle and polarity are configurable

- PWM2/3 both support 1 channel and support mapping

- PWM4 supports 1 channel

- Support timing mode

- Operating voltage: 2.7V ~5.5V

- ➢ Operating temperature: -40°C ~105℃

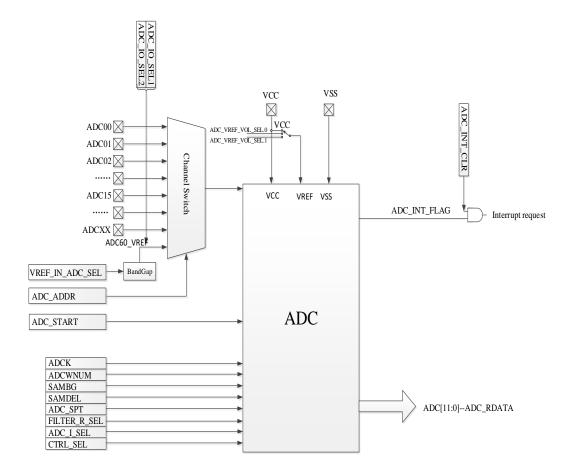

- High precision 12-bit ADC

- Up to 59 analog input channels

- Reference voltage: VCC/2V/4V

- Single conversion mode

- > Interrupt

- 26 interrupt sources

- ➢ 4-level interrupt priority can be configured

- > Timer

- 16-bit Timer0/1/2/3

- Timer2 clock source: LIRC 32k, XTAL 32768Hz/4MHz/8MHz

- Watchdog timer, overflow time from 18ms to 2.304s

- SysTick timer

- > LED Driver

- Support up to 8COM x 16SEG (1/8~8/8 duty cycle)

- LCD Driver

- 4 COM x 28 SEG (1/4 duty cycle, 1/3 bias)

- 5 COM x 27 SEG (1/5 duty cycle, 1/3 bias)

- $\circ$  6 COM x 26 SEG (1/6 duty cycle, 1/3 bias or 1/4 bias)

- 8 COM x 24 SEG (1/8 duty cycle, 1/4 bias)

- Touch key

- The sensitivity of each key can be set independently

- Capacitive keys can be reused as GPIO

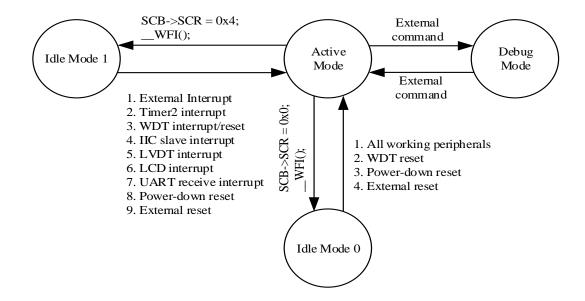

- > Low power management

- $\circ \quad \ \ Idle \ mode \ 0, power \ consumption \ 1.7mA@5V \ typical$

- Idle mode 1, power consumption 8.0µA@5V typical

- > Cyclic redundancy check unit

- CRC8/16/32

- > 96-bit/128-bit chip unique identification code

- Serial two-wire debugging interface SWD, PGC/PGD programming

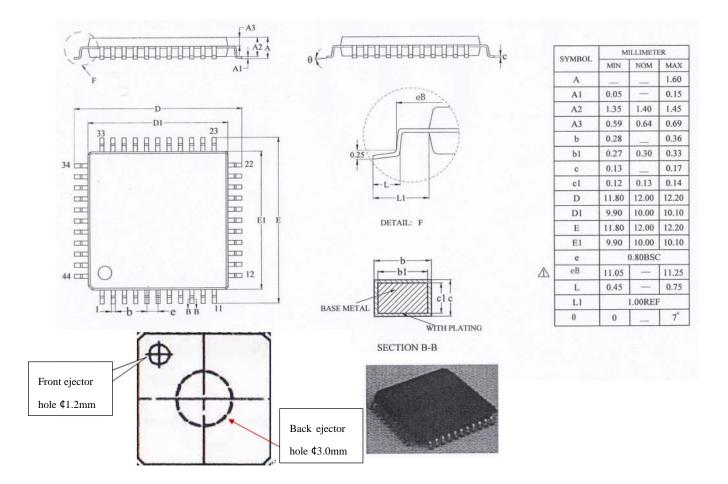

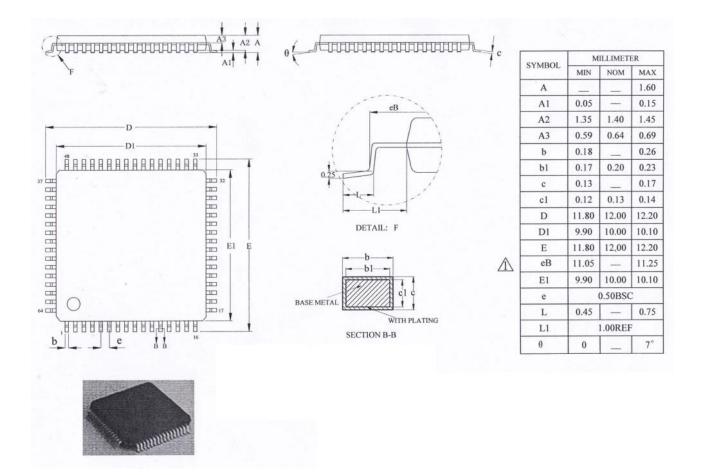

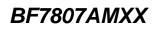

- Package

- LQFP44/LQFP64

#### 1.2. Overview

The BF7807AMXX adopts ARM Cortex-M0+ core, 32-bit high-performance microcontroller. The Cortex-M0+ core is based on the ARMv6-M architecture and supports the Thumb instruction set.

The BF7807AMXX includes peripheral watchdog, LED row and column matrix driver, LCD driver, capacitive touch key detection, IIC master-slave, SPI master-slave, multi-channel UART, PWM, Timer0, Timer1, Timer2, Timer3, 12bit successive approximation ADC, low-voltage detection, power-down reset, low-power management and other modules.

The BF7807AMXX integrates multiple capacitive detection channels, which can be used to detect proximity sensing or touch, and realize various applications such as keys, scroll wheels, and sliders. The BF7807AMXX can configure the corresponding function register to adjust the sensitivity of the capacitance detection channel.

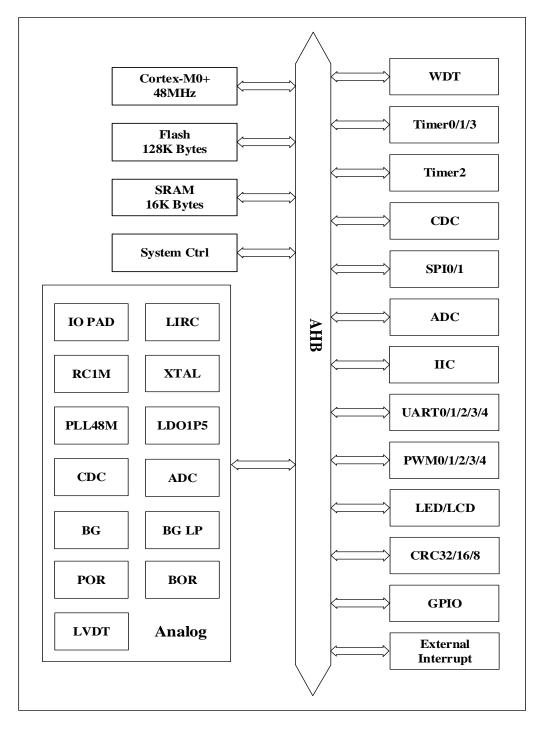

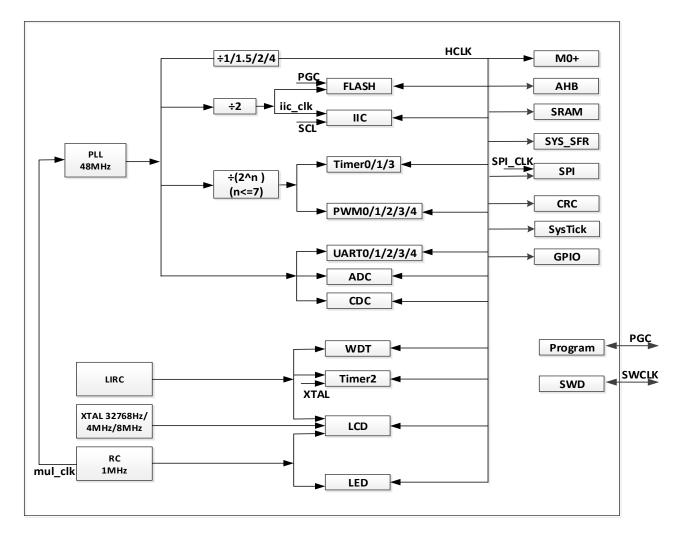

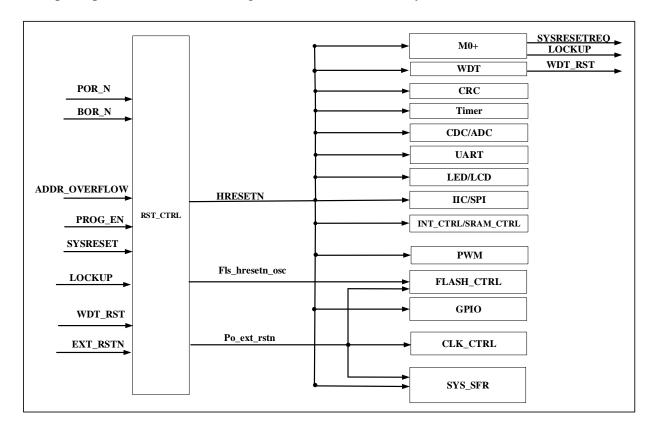

# 1.3. System architecture

System architecture

# 1.4. Memory map

| 0x500A_FFFF | External Interrupt  |         |               |        |

|-------------|---------------------|---------|---------------|--------|

| 0x500A_0100 | <b>.</b>            |         |               |        |

| 0x500A_0000 | GPIO                | r       | _             |        |

|             | CRC                 |         | 0x5005_0900   | PWM4   |

| 0x5009_0000 |                     |         | 0x5005_0800   | PWM3   |

|             | LED/LCD             |         | 0x5005_0700   | PWM2   |

| 0x5008_0000 |                     |         | 0x5005_0600   | PWM1   |

| 0x5007_0000 | ADC                 |         | 0x5005_0500   | PWM0   |

| 0.0007_0000 | CDC                 |         | 0x5005_0400   | WDT    |

| 0x5006_0000 | СЪС                 |         | 0x5005_0300   | Timer3 |

|             | Timer0~3/WDT/PWM0~4 | <b></b> | 0x5005_0200   | Timer2 |

| 0x5005_0000 |                     |         | 0x5005_0100   | Timer1 |

| 0 5004 0000 | IIC                 |         | - 0x5005_0000 | Timer0 |

| 0x5004_0000 |                     |         |               |        |

| 0x5003_0000 | UART0~4             |         | 0x5003_0400   | UART4  |

| _           | SPI0/1              |         | 0x5003_0300   | UART3  |

| 0x5002_0000 |                     |         | 0x5003_0200   | UART2  |

| 0 5001 0000 | FLASH_CTRL          |         | 0x5003_0100   | UART1  |

| 0x5001_0000 |                     |         | 0x5003_0000   | UARTO  |

| 0x5000_001C | LVDT                |         | 0x5002_0100   | SPI1   |

|             | CVC CTDI            | ļ       | 0x5002_0000   | SPI0   |

| 0x5000_0000 | SYS_CTRL            |         |               |        |

|             |                     |         |               |        |

|             | Reserved            |         |               |        |

| 0x2000_4000 |                     |         |               |        |

|             | <b>GDAN</b>         |         |               |        |

|             | SRAM                |         |               |        |

| 0x2000_0000 |                     |         |               |        |

|             | Reserved            |         |               |        |

|             | Keserveu            |         |               |        |

| 0x0003_0000 |                     |         |               |        |

|             | FLASH IP/ FLASH NVR |         |               |        |

|             |                     |         |               |        |

| 0x0000_0000 |                     |         |               |        |

Address division map

| Address range             | Size(Bytes) | Module             |

|---------------------------|-------------|--------------------|

| 0x0000_0000 ~ 0x0002_FFFF | 192K        | FLASH IP/FLASH NVR |

| 0x2000_0000 ~ 0x2000_3FFF | 16K         | SRAM               |

| 0x5000_0000 ~ 0x5000_001B | CAV         | SYS_CTRL           |

| 0x5000_001C~ 0x5000_FFFF  | 64K         | LVDT               |

| 0x5001_0000 ~ 0x5001_FFFF | 64K         | FLASH_CTRL         |

| 0x5002_0000 ~ 0x5002_00FF | 256         | SPIO               |

| 0x5002_0100 ~ 0x5002_01FF | 256         | SPI1               |

| 0x5002_0200 ~ 0x5002_FFFF | -           | Reserved           |

| 0x5003_0000 ~ 0x5003_00FF | 256         | UART0              |

| 0x5003_0100 ~ 0x5003_01FF | 256         | UART1              |

| 0x5003_0200 ~ 0x5003_02FF | 256         | UART2              |

| 0x5003_0300 ~ 0x5003_03FF | 256         | UART3              |

| 0x5003_0400 ~ 0x5003_04FF | 256         | UART4              |

| 0x5003_0500 ~ 0x5003_FFFF | -           | Reserved           |

| 0x5004_0000 ~ 0x5004_FFFF | 64K         | IIC                |

| 0x5005_0000 ~ 0x5005_00FF | 256         | Timer0             |

| 0x5005_0100 ~ 0x5005_01FF | 256         | Timer1             |

| 0x5005_0200 ~ 0x5005_02FF | 256         | Timer2             |

| 0x5005_0300 ~ 0x5005_03FF | 256         | Timer3             |

| 0x5005_0400 ~ 0x5005_04FF | 256         | WDT                |

| 0x5005_0500 ~ 0x5005_05FF | 256         | PWM0               |

| 0x5005_0600 ~ 0x5005_06FF | 256         | PWM1               |

| 0x5005_0700 ~ 0x5005_07FF | 256         | PWM2               |

| 0x5005_0800 ~ 0x5005_08FF | 256         | PWM3               |

| 0x5005_0900 ~ 0x5005_09FF | 256         | PWM4               |

| 0x5005_0A00 ~ 0x5005_FFFF | -           | Reserved           |

| 0x5006_0000 ~ 0x5006_FFFF | 64K         | CDC                |

| 0x5007_0000 ~ 0x5007_FFFF | 64K         | ADC                |

| 0x5008_0000 ~ 0x5008_FFFF | 64K         | LED/LCD            |

| 0x5009_0000 ~ 0x5009_FFFF | 64K         | CRC                |

| 0x500A_0000 ~ 0x500A_00FF |             | GPIO               |

| 0x500A_0100 ~ 0x500A_FFFF | 64K         | External Interrupt |

Table Address division

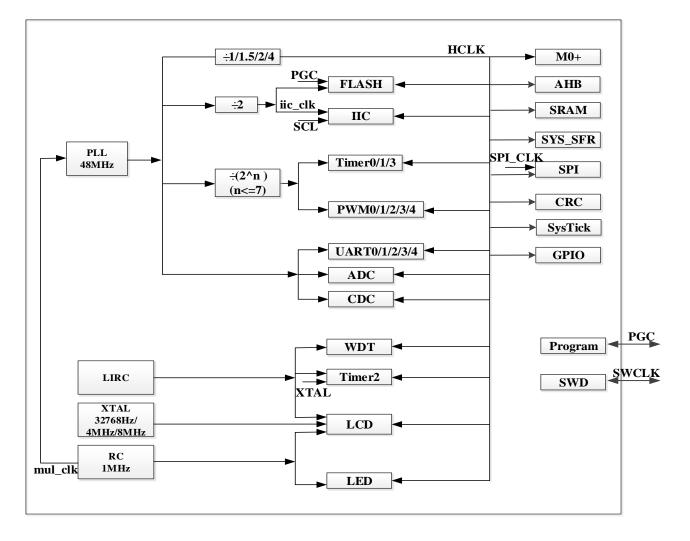

# 1.5. Clock block diagram

Clock block diagram

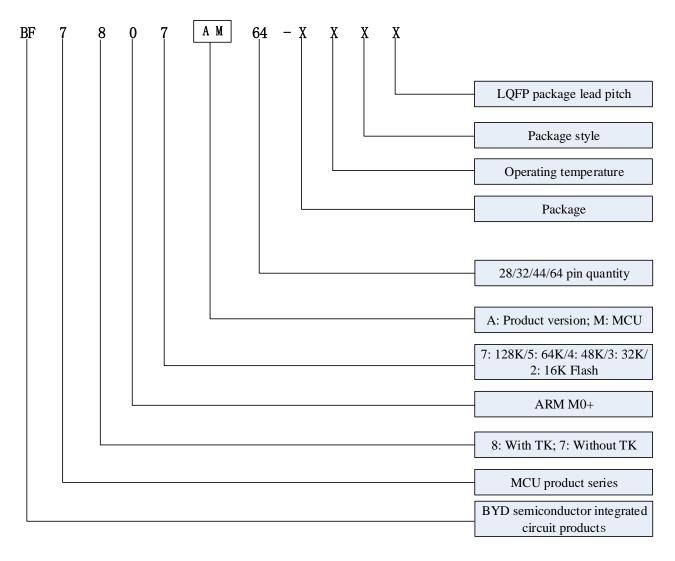

# 1.6. Selection list

|                       |              | BF7807AM44-    | BF7807AM64-    | BF7807AM64-    |

|-----------------------|--------------|----------------|----------------|----------------|

| Moo                   | del          | LJTX           | LJTA           | LJTX           |

| Operating voltage (V) |              | 2.7~5.5        | 2.7~5.5        | 2.7~5.5        |

| Operating free        | quency (Hz)  | 48M            | 48M            | 48M            |

| Co                    | re           | ARM Cortex-M0+ | ARM Cortex-M0+ | ARM Cortex-M0+ |

| C 11                  | FLASH        | 128004B        | 128K           | 128K           |

| Storage module        | DATA         | 512            | 512            | 512            |

| (Bytes)               | SRAM         | 16K            | 16K            | 16K            |

|                       | WDT          | 1              | 1              | 1              |

|                       | Timer0*16bit | 1              | 1              | 1              |

| Timer                 | Timer1*16bit | 1              | 1              | 1              |

|                       | Timer2*16bit | 1              | 1              | 1              |

|                       | Timer3*16bit | 1              | 1              | 1              |

|                       | IIC          | 1              | 1              | 1              |

| Communication         | UART         | 5              | 5              | 5              |

| module                | SPI          | 2              | 2              | 2              |

| GP                    | Ю            | 42             | 59             | 59             |

| KE                    | Y            | 42             | 59             | 59             |

| IN                    | Т            | 42             | 59             | 59             |

| CO                    | М            | 8              | 8              | 8              |

| Analog module         | ADC*12bit    | 42             | 59             | 59             |

| Diamlary madula       | LED ranks    | 8 COM x 16 SEG | 8 COM x 16 SEG | 8COM x 16SEG   |

| Display module        | LCD          | 8 COM x 22 SEG | 8 COM x 24 SEG | 8COM x 24SEG   |

|                       | PWM0*16bit   | 5              | 5              | 5              |

|                       | PWM1*16bit   | 5              | 5              | 5              |

| PWM module            | PWM2*16bit   | 1              | 1              | 1              |

|                       | PWM3*16bit   | 1              | 1              | 1              |

|                       | PWM4*16bit   | -              | 1              | 1              |

| CRC                   |              | CRC8/16/32     | CRC8/16/32     | CRC8/16/32     |

| Package               |              | LQFP44         | LQFP64         | LQFP64         |

|                       |              | (10mm*10mm,    | (10mm*10mm,    | (14mm*14mm,    |

|                       |              | e=0.8mm)       | e=0.5mm)       | e=0.8mm)       |

## **1.7. Pin configuration**

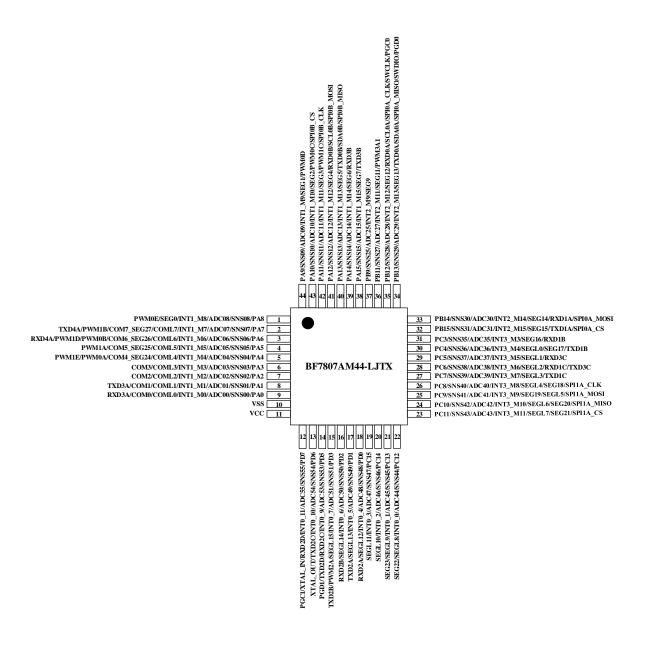

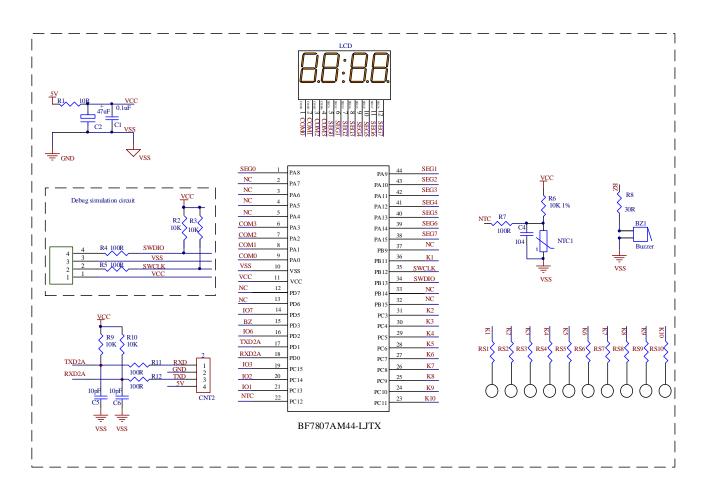

#### 1.7.1. BF7807AM44-LJTX

LQFP44 package pin diagram

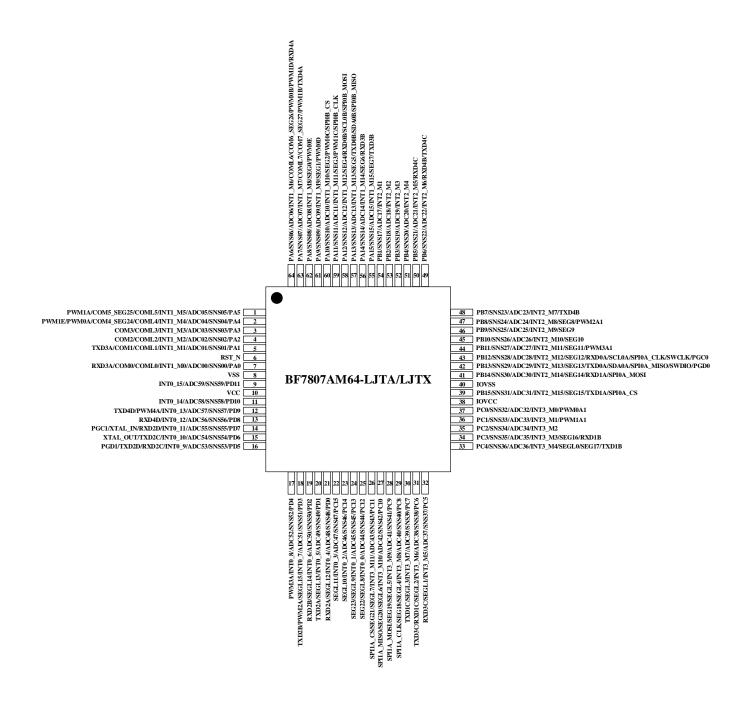

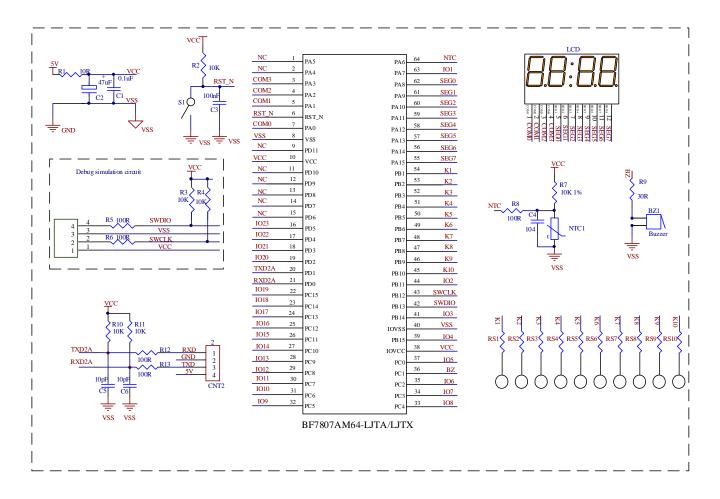

#### 1.7.2. BF7807AM64-LJTA/LJTX

LQFP64 package pin diagram

# **1.8. Pin description**

| BF7807AM64-<br>LJTA/LJTX | BF7807AM44-<br>LJTX | Function description                                       |

|--------------------------|---------------------|------------------------------------------------------------|

|                          |                     | Default function: GPIO <pa5></pa5>                         |

|                          |                     | Other functions: SNS05: Touch key channel                  |

|                          |                     | ADC05: ADC channel                                         |

| 1                        | 4                   | INT1_M5: External interrupt                                |

|                          |                     | COML5: COM of LED row column matrix; Large irrigation port |

|                          |                     | COM5_SEG25: COM of LCD can be shared as SEG                |

|                          |                     | PWM1A: PWM output port                                     |

|                          |                     | Default function: GPIO <pa4></pa4>                         |

|                          |                     | Other functions: SNS04: Touch key channel                  |

|                          |                     | ADC04: ADC channel                                         |

| 2                        | 5                   | INT1_M4: External interrupt                                |

| 2                        | 5                   | COML4: COM of LED row column matrix; Large irrigation port |

|                          |                     | COM4_SEG24: COM of LCD can be shared as SEG                |

|                          |                     | PWM0A: PWM output port                                     |

|                          |                     | PWM1E: PWM output port                                     |

|                          |                     | Default function: GPIO <pa3></pa3>                         |

|                          | 6                   | Other functions: SNS03: Touch key channel                  |

| 3                        |                     | ADC03: ADC channel                                         |

| 3                        |                     | INT1_M3: External interrupt                                |

|                          |                     | COML3: COM of LED row column matrix; Large irrigation port |

|                          |                     | COM3: LCD COM                                              |

|                          | 7                   | Default function: GPIO <pa2></pa2>                         |

|                          |                     | Other functions: SNS02: Touch key channel                  |

| 4                        |                     | ADC02: ADC channel                                         |

| 4                        |                     | INT1_M2: External interrupt                                |

|                          |                     | COML2: COM of LED row column matrix; Large irrigation port |

|                          |                     | COM2: LCD COM                                              |

|                          |                     | Default function: GPIO <pa1></pa1>                         |

|                          |                     | Other functions: SNS01: Touch key channel                  |

|                          |                     | ADC01: ADC channel                                         |

| 5                        | 8                   | INT1_M1: External interrupt                                |

|                          |                     | COML1: COM of LED row column matrix; Large irrigation port |

|                          |                     | COM1: LCD COM                                              |

|                          |                     | TXD3A: Serial port transmission                            |

| 6                        | -                   | RST_N: Reset pin                                           |

|    |    | Default function: GPIO <pa0></pa0>                         |

|----|----|------------------------------------------------------------|

|    |    | Other functions: SNS00: Touch key channel                  |

|    |    | ADC00: ADC channel                                         |

| 7  | 9  | INT1_M0: External interrupt                                |

|    |    | COML0: COM of LED row column matrix; Large irrigation port |

|    |    | COM0: LCD COM                                              |

|    |    | RXD3A: Serial port receiving                               |

| 8  | 10 | Default function: GND <vss></vss>                          |

|    |    | Default function: GPIO <pd11></pd11>                       |

|    |    | Other functions: SNS59: Touch key channel                  |

| 9  | -  | ADC59: ADC channel                                         |

|    |    | INT0_15: External interrupt                                |

| 10 | 11 | Default function: Power supply <vcc></vcc>                 |

|    |    | Default function: GPIO <pd10></pd10>                       |

|    |    | Other functions: SNS58: Touch key channel                  |

| 11 | -  | ADC58: ADC channel                                         |

|    |    | INT0_14: External interrupt                                |

|    |    | Default function: GPIO <pd9></pd9>                         |

|    |    | Other functions: SNS57: Touch key channel                  |

| 12 |    | ADC57: ADC channel                                         |

| 12 | -  | INT0_13: External interrupt                                |

|    |    | PWM4A: PWM output port                                     |

|    |    | TXD4D: Serial port transmission                            |

|    |    | Default function: GPIO <pd8></pd8>                         |

|    |    | Other functions: SNS56: Touch key channel                  |

| 13 | -  | ADC56: ADC channel                                         |

|    |    | INT0_12: External interrupt                                |

|    |    | RXD4D: Serial port receiving                               |

|    |    | Default function: GPIO <pd7></pd7>                         |

|    |    | Other functions: SNS55: Touch key channel                  |

|    |    | ADC55: ADC channel                                         |

| 14 | 12 | INT0_11: External interrupt                                |

|    |    | RXD2D: Serial port receiving                               |

|    |    | XTAL_IN: External crystal input                            |

|    |    | PGC1: Programming port                                     |

|    |    | Default function: GPIO <pd6></pd6>                         |

|    |    | Other functions: SNS54: Touch key channel                  |

| 15 | 13 | ADC54: ADC channel                                         |

|    |    | INTO_10: External interrupt                                |

|    |    | TXD2D: Serial port transmission                            |

|    |    | XTAL_OUT: External crystal oscillator output               |

|    | [        | Default function: GPIO <pd5></pd5>        |

|----|----------|-------------------------------------------|

|    |          |                                           |

|    |          | Other functions: SNS53: Touch key channel |

| 17 | 14       | ADC53: ADC channel                        |

| 16 | 14       | INT0_9: External interrupt                |

|    |          | TXD2D: Serial port transmission           |

|    |          | RXD2C: Serial port receiving              |

|    | l        | PGD1: Programming port                    |

|    |          | Default function: GPIO <pd4></pd4>        |

|    |          | Other functions: SNS52: Touch key channel |

| 17 | -        | ADC52: ADC channel                        |

|    |          | INT0_8: External interrupt                |

| i  |          | PWM3A: PWM output port                    |

|    |          | Default function: GPIO <pd3></pd3>        |

|    |          | Other functions: SNS51: Touch key channel |

|    |          | ADC51: ADC channel                        |

| 18 | 15       | INT0_7: External interrupt                |

|    |          | SEGL15: SEG of LED row column matrix      |

|    |          | TXD2B: Serial port transmission           |

|    |          | PWM2A: PWM output port                    |

|    |          | Default function: GPIO <pd2></pd2>        |

|    |          | Other functions: SNS50: Touch key channel |

| 10 | 16       | ADC50: ADC channel                        |

| 19 |          | INT0_6: External interrupt                |

|    |          | SEGL14: SEG of LED row column matrix      |

|    |          | RXD2B: Serial port receiving              |

|    |          | Default function: GPIO <pd1></pd1>        |

|    |          | Other functions: SNS49: Touch key channel |

| 20 | 17       | ADC49: ADC channel                        |

| 20 | 17       | INT0_5: External interrupt                |

|    |          | SEGL13: SEG of LED row column matrix      |

|    |          | TXD2B: Serial port transmission           |

|    |          | Default function: GPIO <pd0></pd0>        |

|    |          | Other functions: SNS48: Touch key channel |

|    | 10       | ADC48: ADC channel                        |

| 21 | 18       | INTO_4: External interrupt                |

|    |          | SEGL12: SEG of LED row column matrix      |

|    |          | RXD2A: Serial port receiving              |

|    |          | Default function: GPIO <pc15></pc15>      |

|    |          | Other functions: SNS47: Touch key channel |

| 22 | 19       | ADC47: ADC channel                        |

| 22 | .,       | INTO_3: External interrupt                |

|    |          | SEGL11: SEG of LED row column matrix      |

| Li | <u> </u> |                                           |

|          |     | Defect for the ODIO (DC14)                |

|----------|-----|-------------------------------------------|

| 22       |     | Default function: GPIO <pc14></pc14>      |

|          | • • | Other functions: SNS46: Touch key channel |

| 23       | 20  | ADC46: ADC channel                        |

|          |     | INTO_2: External interrupt                |

|          |     | SEGL10: SEG of LED row column matrix      |

|          |     | Default function: GPIO <pc13></pc13>      |

|          |     | Other functions: SNS45: Touch key channel |

| 24       | 21  | ADC45: ADC channel                        |

| 27       | 21  | INT0_1: External interrupt                |

|          |     | SEGL9: SEG of LED row column matrix       |

|          |     | SEG23: SEG of LCD                         |

|          |     | Default function: GPIO <pc12></pc12>      |

|          |     | Other functions: SNS44: Touch key channel |

| 25       | 22  | ADC44: ADC channel                        |

| 25       | 22  | INT0_0: External interrupt                |

|          |     | SEGL8: SEG of LED row column matrix       |

|          |     | SEG22: SEG of LCD                         |

|          |     | Default function: GPIO <pc11></pc11>      |

|          |     | Other functions: SNS43: Touch key channel |

|          |     | ADC43: ADC channel                        |

| 26       | 23  | INT3_M11: External interrupt              |

|          |     | SEGL7: SEG of LED row column matrix       |

|          |     | SEG21: SEG of LCD                         |

|          |     | SPI1A_CS: SPI chip selection signal       |

|          |     | Default function: GPIO <pc10></pc10>      |

|          |     | Other functions: SNS42: Touch key channel |

|          | 24  | ADC42: ADC channel                        |

| 27       |     | INT3_M10: External interrupt              |

|          |     | SEGL6: SEG of LED row column matrix       |

|          |     | SEG20: SEG of LCD                         |

|          |     | SPI1A_MISO: SPI master data input         |

|          | ļ   | Default function: GPIO <pc9></pc9>        |

|          |     | Other functions: SNS41: Touch key channel |

|          |     | ADC41: ADC channel                        |

| 28       | 25  | INT3_M9: External interrupt               |

| 20       | 25  | SEGL5: SEG of LED row column matrix       |

|          |     | SEG19: SEG of LCD                         |

|          |     | SPI1A_MOSI: SPI master data output        |

| <u> </u> |     | Default function: GPIO <pc8></pc8>        |

|          |     | Other functions: SNS40: Touch key channel |

| 29       | 26  | ADC40: ADC channel                        |

|          |     |                                           |

|          |     | INT3_M8: External interrupt               |

|    |    | SEGL4: SEG of LED row column matrix                                |

|----|----|--------------------------------------------------------------------|

|    |    | SEG14: SEG of LCD                                                  |

|    |    | SPI1A_CLK: SPI clock                                               |

|    |    | Default function: GPIO <pc7></pc7>                                 |

|    |    |                                                                    |

|    |    | Other functions: SNS39: Touch key channel<br>ADC39: ADC channel    |

| 30 | 27 |                                                                    |

|    |    | INT3_M7: External interrupt<br>SEGL3: SEG of LED row column matrix |

|    |    |                                                                    |

|    |    | TXD1C: Serial port transmission                                    |

|    |    | Default function: GPIO <pc6></pc6>                                 |

|    |    | Other functions: SNS38: Touch key channel                          |

|    | 20 | ADC38: ADC channel                                                 |

| 31 | 28 | INT3_M6: External interrupt                                        |

|    |    | SEGL2: SEG of LED row column matrix                                |

|    |    | RXD1C: Serial port receiving                                       |

|    |    | TXD3C: Serial port transmission                                    |

|    |    | Default function: GPIO <pc5></pc5>                                 |

|    |    | Other functions: SNS37: Touch key channel                          |

| 32 | 29 | ADC37: ADC channel                                                 |

| 52 |    | INT3_M5: External interrupt                                        |

|    |    | SEGL1: SEG of LED row column matrix                                |

|    |    | RXD3C: Serial port receiving                                       |

|    |    | Default function: GPIO <pc4></pc4>                                 |

|    |    | Other functions: SNS36: Touch key channel                          |

|    |    | ADC36: ADC channel                                                 |

| 33 | 30 | INT3_M4: External interrupt                                        |

|    |    | SEGL0: SEG of LED row column matrix                                |

|    |    | SEG17: SEG of LCD                                                  |

|    |    | TXD1B: Serial port transmission                                    |

|    |    | Default function: GPIO <pc3></pc3>                                 |

|    |    | Other functions: SNS35: Touch key channel                          |

| 24 | 21 | ADC35: ADC channel                                                 |

| 34 | 31 | INT3_M3: External interrupt                                        |

|    |    | SEG16: SEG of LCD                                                  |

|    |    | RXD1B: Serial port receiving                                       |

|    |    | Default function: GPIO <pc2></pc2>                                 |

| 25 |    | Other functions: SNS34: Touch key channel                          |

| 35 | -  | ADC34: ADC channel                                                 |

|    |    | INT3_M2: External interrupt                                        |

|    |    | Default function: GPIO <pc1></pc1>                                 |

| 36 | -  | Other functions: SNS33: Touch key channel                          |

|    |    | ADC33: ADC channel                                                 |

|    |    | ADC33: ADC channel                                                 |

|    |    | INT2 M1: External interment               |

|----|----|-------------------------------------------|

|    |    | INT3_M1: External interrupt               |

|    |    | PWM1A1: PWM output port                   |

|    |    | Default function: GPIO <pc0></pc0>        |

| 27 |    | Other functions: SNS32: Touch key channel |

| 37 | -  | ADC32: ADC channel                        |

|    |    | INT3_M0: External interrupt               |

|    |    | PWM0A1: PWM output port                   |

| 38 | -  | Default function: IOVCC                   |

|    |    | Default function: GPIO <pb15></pb15>      |

|    |    | Other functions: SNS31: Touch key channel |

|    |    | ADC31: ADC channel                        |

| 39 | 32 | INT2_M15: External interrupt              |

|    |    | SEG15: SEG of LCD                         |

|    |    | SPI0A_CS: SPI chip selection signal       |

|    |    | TXD1A: Serial port transmission           |

| 40 | -  | Default function: IOVSS                   |

|    |    | Default function: GPIO <pb14></pb14>      |

|    |    | Other functions: SNS30: Touch key channel |

|    |    | ADC30: ADC channel                        |

| 41 | 33 | INT2_M14: External interrupt              |

|    |    | SEG14: SEG of LCD                         |

|    |    | SPI0A_ MOSI: SPI master data output       |

|    |    | RXD1A: Serial port receiving              |

|    |    | Default function: GPIO <pb13></pb13>      |

|    |    | Other functions: SNS29: Touch key channel |

|    |    | ADC29: ADC channel                        |

|    |    | INT2_M13: External interrupt              |

| 42 | 34 | SEG13: SEG of LCD                         |

| 42 | 54 | SPI0A_ MISO: SPI master data input        |

|    |    | TXD0A: Serial port transmission           |

|    |    | SDA0A: Serial data line of IIC            |

|    |    | SWDIO: Data input /output                 |

|    |    | PGD0: Programming port                    |

|    |    | Default function: GPIO <pb12></pb12>      |

|    |    | Other functions: SNS28: Touch key channel |

|    |    | ADC28: ADC channel                        |

|    |    | INT2_M12: External interrupt              |

| 43 | 35 | SEG12: SEG of LCD                         |

|    |    | SPI0A_ CLK: SPI clock                     |

|    |    | RXD0A: Serial port receiving              |

|    |    | SCL0A: Serial clock line of IIC           |

|    |    | SWCLK: Clock signal                       |

|    |    |                                           |

|    |    | PGC0: Programming port                    |

|----|----|-------------------------------------------|

|    |    | Default function: GPIO <pb11></pb11>      |

|    |    | Other functions: SNS27: Touch key channel |

|    |    | ADC27: ADC channel                        |

| 44 | 36 | INT2_M11: External interrupt              |

|    |    | SEG11: SEG of LCD                         |

|    |    | PWM3A1: PWM output port                   |

|    |    | Default function: GPIO <pb10></pb10>      |

|    |    | Other functions: SNS26: Touch key channel |

| 45 | -  | ADC26: ADC channel                        |

|    |    | INT2_M10: External interrupt              |

|    |    | SEG10: SEG of LCD                         |

|    |    | Default function: GPIO <pb9></pb9>        |

|    |    | Other functions: SNS25: Touch key channel |

| 46 | 37 | ADC25: ADC channel                        |

|    |    | INT2_M9: External interrupt               |

|    |    | SEG9: SEG of LCD                          |

|    |    | Default function: GPIO <pb8></pb8>        |

|    |    | Other functions: SNS24: Touch key channel |

| 47 | _  | ADC24: ADC channel                        |

| ., |    | INT2_M8: External interrupt               |

|    |    | SEG8: SEG of LCD                          |

|    |    | PWM2A1: PWM output port                   |

|    |    | Default function: GPIO <pb7></pb7>        |

|    |    | Other functions: SNS23: Touch key channel |

| 48 | -  | ADC23: ADC channel                        |

|    |    | INT2_M7: External interrupt               |

|    |    | TXD4B: Serial port transmission           |

|    |    | Default function: GPIO <pb6></pb6>        |

|    |    | Other functions: SNS22: Touch key channel |

| 49 | -  | ADC22: ADC channel                        |

| _  |    | INT2_M6: External interrupt               |

|    |    | RXD4B: Serial port receiving              |

|    |    | TXD4C: Serial port transmission           |

|    |    | Default function: GPIO <pb5></pb5>        |

|    |    | Other functions: SNS21: Touch key channel |

| 50 | -  | ADC21: ADC channel                        |

|    |    | INT2_M5: External interrupt               |

|    |    | RXD4C: Serial port receiving              |

|    |    | Default function: GPIO <pb4></pb4>        |

| 51 | -  | Other functions: SNS20: Touch key channel |

|    |    | ADC20: ADC channel                        |

|    |    | INT2_M4: External interrupt                   |

|----|----|-----------------------------------------------|

|    |    | Default function: GPIO <pb3></pb3>            |

| 52 |    | Other functions: SNS19: Touch key channel     |

|    | -  | ADC19: ADC channel                            |

|    |    | INT2_M3: External interrupt                   |

|    |    | Default function: GPIO <pb2></pb2>            |

| 50 |    | Other functions: SNS18: Touch key channel     |

| 53 | -  | ADC18: ADC channel                            |

|    |    | INT2_M2: External interrupt                   |

|    |    | Default function: GPIO <pb1></pb1>            |

| 54 |    | Other functions: SNS17: Touch key channel     |

| 54 | -  | ADC17: ADC channel                            |

|    |    | INT2_M1: External interrupt                   |

|    |    | Default function: GPIO <pa15></pa15>          |

|    |    | Other functions: SNS15: Touch the key channel |

| 55 | 38 | ADC15: ADC channel                            |

| 55 | 50 | INT1_M15: External interrupt                  |

|    |    | SEG7: SEG of LCD                              |

|    |    | TXD3B: Serial port transmission               |

|    |    | Default function: GPIO <pa14></pa14>          |

|    | 39 | Other functions: SNS14: Touch key channel     |

| 56 |    | ADC14: ADC channel                            |

| 20 |    | INT1_M14: External interrupt                  |

|    |    | SEG6: SEG of LCD                              |

|    |    | RXD3B: Serial port receiving                  |

|    |    | Default function: GPIO <pa13></pa13>          |

|    |    | Other functions: SNS13: Touch key channel     |

|    |    | ADC13: ADC channel                            |

| 57 | 40 | INT1_M13: External interrupt                  |

|    |    | SEG5: SEG of LCD                              |

|    |    | SPI0B_MISO: SPI master data input             |

|    |    | TXD0B: Serial port transmission               |

|    |    | SDA0B: Serial data line of IIC                |

|    |    | Default function: GPIO <pa12></pa12>          |

|    |    | Other functions: SNS12: Touch key channel     |

|    |    | ADC12: ADC channel                            |

| 58 | 41 | INT1_M12: External interrupt                  |

|    |    | SEG4: SEG of LCD                              |

|    |    | SPI0B_MOSI: SPI master data output            |

|    |    | RXD0B: Serial port receiving                  |

|    |    | SCL0B: Serial clock line of IIC               |

|    |    | Default function: GPIO <pa11></pa11>                       |

|----|----|------------------------------------------------------------|

| 59 |    | Other functions: SNS11: Touch key channel                  |

|    |    | ADC11: ADC channel                                         |

|    | 42 | INT1_M11: External interrupt                               |

| 39 | 42 | SEG3: SEG of LCD                                           |

|    |    |                                                            |

|    |    | PWM1C: PWM output port                                     |

|    |    | SPI0B_CLK: SPI clock                                       |

|    |    | Default function: GPIO <pa10></pa10>                       |

|    |    | Other functions: SNS10: Touch key channel                  |

|    |    | ADC10: ADC channel                                         |

| 60 | 43 | INT1_M10: External interrupt                               |

|    |    | SEG2: SEG of LCD                                           |

|    |    | PWM0C: PWM output port                                     |

|    |    | SPI0B_CS: SPI chip selection signal                        |

|    |    | Default function: GPIO <pa9></pa9>                         |

|    |    | Other functions: SNS09: Touch key channel                  |

| 61 | 44 | ADC09: ADC channel                                         |

| 01 |    | INT1_M9: External interrupt                                |

|    |    | SEG1: SEG of LCD                                           |

|    |    | PWM0D: PWM output port                                     |

|    |    | Default function: GPIO <pa8></pa8>                         |

|    | 1  | Other functions: SNS08: Touch key channel                  |

| 62 |    | ADC08: ADC channel                                         |

| 02 |    | INT1_M8: External interrupt                                |

|    |    | SEG0: SEG of LCD                                           |

|    |    | PWM0E: PWM output port                                     |

|    |    | Default function: GPIO <pa7></pa7>                         |

|    |    | Other functions: SNS07: Touch key channel                  |

|    | 2  | ADC07: ADC channel                                         |

| 63 |    | INT1_M7: External interrupt                                |

|    |    | COML7: COM of LED row column matrix; Large irrigation port |

|    |    | COM7_SEG27: COM OF LCD can be shared as SEG                |

|    |    | TXD4A: Serial port transmission                            |

|    |    | Default function: GPIO <pa6></pa6>                         |

|    |    | Other functions: SNS06: Touch key channel                  |

|    |    | ADC06: ADC channel                                         |

|    |    | INT1_M6: External interrupt                                |

| 64 | 3  | COML6: COM of LED row column matrix; Large irrigation port |

|    |    | COM6_SEG26: COM OF LCD can be shared as SEG                |

|    |    | PWM0B: PWM output port                                     |

|    |    | PWM1D: PWM output port                                     |

|    |    | RXD4A: Serial port receiving                               |

|    |    | KAD4A. Schar politicici vilig                              |

# **2** Electrical characteristics

## 2.1. Limit parameters

| Ch-al            | Demonstern                           | Test ( | Condition | Min     | Turnical | Max     | Unit |  |

|------------------|--------------------------------------|--------|-----------|---------|----------|---------|------|--|

| Symbol           | Parameter                            | VCC    | Condition |         | Typical  | wax     | Cint |  |

| VCC              | Supply voltage when operating        | -      | -         | VSS+2.7 | -        | VSS+5.5 | v    |  |

| T <sub>STG</sub> | Storage temperature                  | -      | -         | -40     | -        | 125     | °C   |  |

| Та               | Operating temperature                | -      | -         | -40     | -        | 105     | °C   |  |

| Vin              | I/O input voltage                    | -      | -         | VSS-0.5 | -        | VCC+0.5 | V    |  |

| Iola             | IoL total current                    | -      | -         |         | 130      |         | mA   |  |

| I <sub>OHA</sub> | I <sub>OH</sub> total current        | -      | -         | -130    |          |         | mA   |  |

| ESD(HBM)         | Port electrostatic discharge voltage | -      | -         | -8      | -        | 8       | kV   |  |

Note: Exceeding the range specified by the limit parameters will cause damage to the chip. It is impossible to predict the working state of the chip outside the above marked range, and if it works under the conditions outside the marked range for a long time, it may affect the reliability of the chip.

## 2.2. AC characteristics

| S-mah al                                | Devenuetor     | Test C    | onditions    | Min  | Trunical    | Mar  | TI:4 |  |

|-----------------------------------------|----------------|-----------|--------------|------|-------------|------|------|--|

| Symbol                                  | Parameter      | VCC       | Temperature  | Min  | Typical     | Max  | Unit |  |

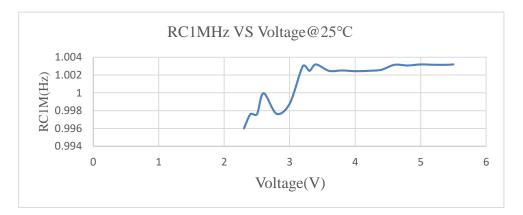

|                                         |                | 517       | -20°C~65°C   | -1%  | 1           | +1%  |      |  |

| £                                       | Internal high- | 5V        | -40°C ~105°C | -3%  | 1           | +3%  | MII- |  |

| f <sub>RC1M</sub> speed R(<br>oscillato | speed RC       | 2711 5 51 | 25°C         | -1%  | 1           | +1%  | MHz  |  |

|                                         | oscillator     | 2.7V~5.5V | -40°C ~105°C | -3%  | 1           | +3%  |      |  |

|                                         |                | 517       | -20°C~65°C   | -1%  | 48/32/24/12 | +1%  |      |  |

| c                                       |                | 5V        | -40°C ~105°C | -3%  | 48/32/24/12 | +3%  | NATT |  |

| f <sub>HCLK</sub>                       | System clock   |           | 25°C         | -1%  | 48/32/24/12 | +1%  | MHz  |  |

|                                         |                | 2.7V~5.5V | -40°C ~105°C | -3%  | 48/32/24/12 | +3%  |      |  |

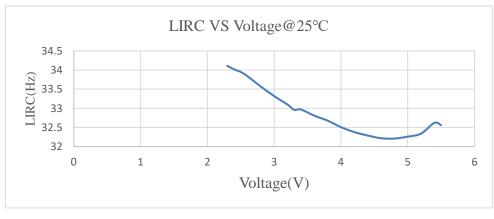

|                                         | Internal low   | 517       | 25°C         | -10% | 32          | +10% |      |  |

| f <sub>LIRC</sub>                       | speed RC       | 5V        | -40°C ~105°C | -25% | 32          | +25% | kHz  |  |

|                                         | oscillator     | 2.7V~5.5V | 25°C         | -20% | 32          | +20% |      |  |

## f<sub>RC1M</sub> voltage graph

#### $f_{LIRC} \ voltage \ graph$

$f_{\mbox{\sc LIRC}}$  temperature curve

## **2.3. DC characteristics**

|                     |                                       |          |                             |         |         | Та      | a=25°C |  |

|---------------------|---------------------------------------|----------|-----------------------------|---------|---------|---------|--------|--|

| Symbol              | Donomotor                             | Tes      | t Condition                 | Min     | Typical | Max     | Unit   |  |

| Symbol              | Parameter                             | VCC      | Condition                   | IVIIII  | туріса  | WIAX    | Omt    |  |

| VCC                 | Operating voltage                     | -        | -                           | 2.7     | -       | 5.5     | V      |  |

|                     |                                       | 3.3V     | f <sub>HCLK</sub> =48MHz,   | -       | 5.0     | 6.5     |        |  |

|                     |                                       | 5V       | all peripherals off         | -       | 5.2     | 6.7     |        |  |

|                     |                                       | 3.3V     | f <sub>HCLK</sub> =32MHz,   | -       | 4.4     | 5.7     |        |  |

| T                   |                                       | 5V       | all peripherals off         | -       | 4.6     | 6.0     |        |  |

| $I_{OP1}$           | Active mode current                   | 3.3V     | f <sub>HCLK</sub> =24MHz,   | -       | 3.8     | 4.9     | mA     |  |

|                     |                                       | 5V       | all peripherals off         | -       | 4.0     | 5.2     |        |  |

|                     |                                       | 3.3V     | f <sub>HCLK</sub> =12MHz,   | -       | 2.8     | 3.6     |        |  |

|                     |                                       | 5V       | all peripherals off         | -       | 3.0     | 3.9     |        |  |

| T                   |                                       | 3.3V     | SCR = 0x0, all              | -       | 1.6     | 2.0     |        |  |

| $I_{STB0}$          | Idle mode 0 current                   | 5V       | peripherals off             | -       | 1.7     | 2.2     | mA     |  |

| T                   | <b>T</b> 11 1 1                       | 3.3V     | SCR = 0x4, all              | -       | 7.8     | 10.1    |        |  |

| $I_{STB1}$          | Idle mode 1 current                   | 5V       | peripherals off             | -       | 8.0     | 10.4    | μA     |  |

| V <sub>IL</sub>     | Input low voltage                     | 2.7~5.5V | -                           | -       | -       | 0.3*VCC | V      |  |

| V <sub>IH</sub>     | Input high voltage                    | 2.7~5.5V | -                           | 0.7*VCC | -       | -       | V      |  |

| V <sub>INTL</sub>   | INT input low<br>voltage              | 2.7~5.5V | -                           | -       | -       | 0.3*VCC | v      |  |

| V <sub>INTH</sub>   | INT input high<br>voltage             | 2.7~5.5V | -                           | 0.7*VCC | -       | -       | v      |  |

| V <sub>OL</sub>     | Output low voltage                    | 5V       | I <sub>OL</sub> =75mA       | -       | -       | 0.1*VCC | V      |  |

| V <sub>OH</sub>     | Output high voltage                   | 5V       | I <sub>OH</sub> =16mA       | 0.9VCC  | -       | -       | V      |  |

| Iol                 | IO sink current                       | 5V       | V <sub>OL</sub> =0.1VCC     | 53      | 75      | 97      | mA     |  |

| I <sub>OH</sub>     | IO source current                     | 5V       | V <sub>OH</sub> =0.9VCC     | 11      | 16      | 20      | mA     |  |

| I <sub>COM</sub>    | PA0-PA7 high<br>current               | 5V       | V <sub>OL</sub> =0.1VCC     | -       | 130     | -       | mA     |  |

| I <sub>SPI_OL</sub> | SPI high-speed mode<br>sink current   | 5V       | V <sub>SPI_OL</sub> =0.1VCC | -       | 6.0     | -       | mA     |  |

| I <sub>SPI_OH</sub> | SPI high-speed mode source current    | 5V       | V <sub>SPI_OH</sub> =0.9VCC | -       | 5.0     | -       | mA     |  |

| I <sub>Leak</sub>   | Input leakage current                 | 5V       | -                           | -       | 1       | 5       | μΑ     |  |

| $R_{\rm PH}$        | IO/RST_N internal<br>pull-up resistor | 5V       | _                           | 23      | 33      | 42      | kΩ     |  |

| S-mah al          | Deveneter              |     | Test Condition                                                                  | Min    | Tunical | Max  | Unit |  |

|-------------------|------------------------|-----|---------------------------------------------------------------------------------|--------|---------|------|------|--|

| Symbol            | Parameter              | VCC | Condition                                                                       | IVIIII | Typical | wiax | Cint |  |

| I <sub>CDC</sub>  | CDC operating current  | 5V  | f <sub>HCLK</sub> =48MHz, enable<br>CDC, open six channels                      | -      | 0.6     | -    | mA   |  |

| I <sub>ADC</sub>  | ADC operating current  | 5V  | f <sub>HCLK</sub> =48MHz, enable<br>ADC, open one channel                       | -      | 2.7     | -    | mA   |  |

| I <sub>PWM</sub>  | PWM operating current  | 5V  | f <sub>HCLK</sub> =48MHz, enable<br>PWM0, output 4kHz<br>waveform               | -      | 0.6     | -    | mA   |  |

| I <sub>LVDT</sub> | LVDT operating current | 5V  | f <sub>HCLK</sub> =48MHz, enable<br>LVDT, configure<br>detection parameter 2.7V | -      | 0.6     | -    | mA   |  |

# **2.4. ADC characteristics**

|                   |                                 |     |                                                              |        |           |                  | Ta=25°C |

|-------------------|---------------------------------|-----|--------------------------------------------------------------|--------|-----------|------------------|---------|

| Same al           | Davamatar                       | Те  | est Condition                                                | Min    | Tunical   | Max              | Unit    |

| Symbol            | Parameter                       | VCC | Condition                                                    | IVIIII | Typical   | Max              | Umt     |

| V <sub>ADC</sub>  | Supply voltage                  | -   | -                                                            | 2.7    | -         | 5.5              | V       |

| N <sub>R</sub>    | Precision                       | -   | -                                                            | -      | 9         | 10               | Bit     |

| V <sub>ADCI</sub> | ADC input voltage               | -   | -                                                            | VSS    |           | V <sub>REF</sub> | v       |

| р                 | ADC input                       | 51/ | No RC filtering                                              | 1.2    | 3.2       | 17.5             | 1-0     |

| R <sub>ADCI</sub> | resistance                      | 5V  | RC filtering                                                 | 10     | 14.2      | 31.5             | kΩ      |

| I <sub>ADC</sub>  | ADC operating current           | 5V  | f <sub>HCLK</sub> =48MHz,<br>enable ADC,<br>open one channel | -      | 2.7       |                  | mA      |

| I <sub>ADCI</sub> | A/D input current               | -   | -                                                            | -      | -         | 1                | μΑ      |

| DNL               | Differential nonlinearity error | 5V  | -                                                            | -      | <u>+4</u> | ±6               | LSB     |

| INL               | Integral nonlinearity error     | 5V  | -                                                            | -      | <u>+4</u> | ±6               | LSB     |

| $t_1$             | ADC sampling time               | -   | -                                                            | 0.5    | -         | -                | μs      |

| t <sub>ADC</sub>  | ADC conversion time             | -   | -                                                            | 2.875  | -         | -                | μs      |

| RESO              | Resolution                      | -   | -                                                            |        | 12        |                  | Bit     |

| N <sub>ADC</sub>  | Input channel                   | -   | -                                                            | -      | -         | 59               | Channel |

# **2.5. Memory characteristics**

|                    |                          |     |                                                                                          |        |         | ]   | Ta=25°C |

|--------------------|--------------------------|-----|------------------------------------------------------------------------------------------|--------|---------|-----|---------|

| Samph al           | Danamatan                |     | <b>Test Condition</b>                                                                    | Min    | Tunical | Max | Unit    |

| Symbol             | Parameter                | VCC | Condition                                                                                | 101111 | Typical | wax | Umt     |

| EC                 | Erase and write times    | 5V  | -                                                                                        | 20000  | -       | -   | Cycle   |

| t <sub>RET</sub>   | Data retention period    | -   | -                                                                                        | 100    | -       | -   | Year    |

| terase             | Page erase<br>time       | 5V  | fHCLK=48MHz, in the while,<br>the main memory block is<br>page erased                    | -      | 4.5     | -   | ms      |

| t <sub>PROG</sub>  | Programming<br>time      | 5V  | fHCLK=48MHz, in the while,<br>a word is written to the main<br>memory block              | -      | 750     | -   | ns      |

| I <sub>ERASE</sub> | Page erase<br>current 5V |     | f <sub>HCLK</sub> =48MHz, in the while,<br>the main memory block is<br>page erased       | -      | 1.0     | -   | mA      |

| I <sub>PROG</sub>  | Programming current      | 5V  | f <sub>HCLK</sub> =48MHz, in the while,<br>a word is written to the main<br>memory block | -      | 1.2     | -   | mA      |

# 3 System control (SYS\_CTRL)

## **3.1. Clock description**

The clock control module mainly controls the system clock and peripheral clock. It can configure different system clock frequency divisions, and can enable or disable peripheral clocks. Clock source:

- Internal high-speed RC oscillator: RC 1MHz

- Internal low-speed RC oscillator: LIRC 32kHz

- External crystal oscillator: 32768Hz/4MHz/8MHz

- RC1M multiplication to get PLL clock: PLL multiplied clock

The BF7807AMXX series clocks are defined as follows:

- **RC1M:** Internal high-speed RC oscillator, LED/LCD module working clock, frequency multiplier (mul\_clk) to get PLL48MHz.

- **PLL48M:** System clock source, CDC/ADC/UART module working clock.

- HCLK: System clock, AHB bus peripheral clock, 48MHz/32MHz/24MHz/12MHz frequency optional.

- **PLL48M divide by 2:** FLASH programming clock, IIC digital filter clock and IIC master working clock(iic\_clk).

- PLL48M 1~128 frequency division: Timer0/Timer1/Timer3/PWM module working clock.

- LIRC 32kHz: Internal low-speed RC oscillator, WDT/Timer2/LCD module clock source.

- XTAL 32768Hz /4MHz /8MHz: External crystal oscillator, Timer2/LCD module clock source.

- **PGC:** The clock within 5M is used as the FLASH programming clock source.

- SCL: The highest 400kHz clock is used as the IIC slave communication clock source.

- SPI\_CLK: The highest 4MHz clock is used as the slave SPI communication clock source.

- **SWCLK:** Clock within 20M, as the clock source for DEBUG and FLASH programming.

Clock block diagram

## **3.2. Registers**

| Base address: | 0x5000 0000 |

|---------------|-------------|

|---------------|-------------|

| Address offset | Register    | Description                                                               |  |  |  |  |  |

|----------------|-------------|---------------------------------------------------------------------------|--|--|--|--|--|

| 0x00           | CLK_CFG     | Clock configuration register                                              |  |  |  |  |  |

| 0x04           | RCU_EN      | Peripheral module clock control register                                  |  |  |  |  |  |

| 0x0C           | XTAL_HS_SEL | Hysteresis voltage selection of comparator in crystal oscillator register |  |  |  |  |  |

| 0x10           | ANA_CFG     | Analog module switch register                                             |  |  |  |  |  |

| 0x18           | WAKE_CFG    | System wake-up configuration register                                     |  |  |  |  |  |

#### **3.2.1.** Clock registers

#### **3.2.1.1.** Clock configuration register (CLK\_CFG)

Address offset: 0x00

Reset value: 0x0000 0002

| 31 | 30       | 29 | 28 | 27 | 26 | 25   | 24    | 23 | 22 | 21 | 20   | 19    | 18 | 17 | 16 |

|----|----------|----|----|----|----|------|-------|----|----|----|------|-------|----|----|----|

|    | Reserved |    |    |    |    |      |       |    |    |    |      |       |    |    |    |

|    |          |    |    |    |    |      |       |    |    |    |      |       |    |    |    |

| 15 | 14       | 13 | 12 | 11 | 10 | 9    | 8     | 7  | 6  | 5  | 4    | 3     | 2  | 1  | 0  |

|    |          |    |    |    |    |      |       |    |    |    | HCLK | K_SEL |    |    |    |

|    |          |    |    |    |    | Rese | erved |    |    |    |      |       |    |    |    |

| 31:2 | -            | Reserved                                         |

|------|--------------|--------------------------------------------------|

|      | 1:0 HCLK_SEL | HCLK clock frequency division selection register |

|      |              | 00: 48MHz                                        |

| 1:0  |              | 01: 32MHz                                        |

|      |              | 10: 24MHz                                        |

|      |              | 11: 12MHz                                        |

#### **3.2.1.2.** Peripheral module clock control register (RCU\_EN)

This register is a register that allows or prohibits the provision of clocks to peripheral modules. Address offset: 0x04

| Re | Reset value: 0x0000 0001 |    |    |    |    |    |    |    |  |  |  |  |

|----|--------------------------|----|----|----|----|----|----|----|--|--|--|--|

|    | 31                       | 30 | 26 | 25 | 24 |    |    |    |  |  |  |  |

|    | Reserved                 |    |    |    |    |    |    |    |  |  |  |  |

|    |                          |    |    |    |    |    |    |    |  |  |  |  |

|    | 23                       | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |  |

|    |                          |    |    |    |    |    |    |    |  |  |  |  |

RW

| LED_LCD_C | GPIO_CL | CRC_CL | ADC_CL | CDC_CL | WDT_CL | TIMER3_CL | TIMER2_CL |

|-----------|---------|--------|--------|--------|--------|-----------|-----------|

| LKEN      | KEN     | KEN    | KEN    | KEN    | KEN    | KEN       | KEN       |

| RW        | RW      | RW     | RW     | RW     | RW     | RW        | RW        |

| 15        | 14        | 13      | 12      | 11      | 10      | 9       | 8      |

|-----------|-----------|---------|---------|---------|---------|---------|--------|

| TIMER1_CL | TIMER0_CL | PWM4_CL | PWM3_CL | PWM2_CL | PWM1_CL | PWM0_CL | IIC_CL |

| KEN       | KEN       | KEN     | KEN     | KEN     | KEN     | KEN     | KEN    |

| RW        | RW        | RW      | RW      | RW      | RW      | RW      | RW     |

| 7       | 6       | 5       | 4       | 3       | 2        | 1        | 0        |

|---------|---------|---------|---------|---------|----------|----------|----------|

| UART4_C | UART3_C | UART2_C | UART1_C | UART0_C | SPI1_CLK | SPI0_CLK |          |

| LKEN    | LKEN    | LKEN    | LKEN    | LKEN    | EN       | EN       | Reserved |

| RW      | RW      | RW      | RW      | RW      | RW       | RW       |          |

| 31:24        | -              | Reserved                        |  |  |  |  |

|--------------|----------------|---------------------------------|--|--|--|--|

|              |                | LCD/LED module operation enable |  |  |  |  |

| 23           | LED_LCD _CLKEN | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | GPIO module operation enable    |  |  |  |  |

| 22           | GPIO_CLKEN     | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | CRC module operation enable     |  |  |  |  |

| 21 CRC_CLKEN |                | : Work                          |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | ADC module operation enable     |  |  |  |  |

| 20           | ADC_CLKEN      | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | CDC module operation enable     |  |  |  |  |

| 19           | CDC_CLKEN      | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | WDT module operation enable     |  |  |  |  |

| 18           | WDT_CLKEN      | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | TIMER3 module operation enable  |  |  |  |  |

| 17           | TIMER3_CLKEN   | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

|              |                | TIMER2 module operation enable  |  |  |  |  |

| 16           | TIMER2_CLKEN   | 1: Work                         |  |  |  |  |

|              |                | 0: Off, the default is 0        |  |  |  |  |

| 15           | TIMER1_CLKEN   | TIMER1 module operation enable  |  |  |  |  |

|    |              | 1. W. 1                        |  |  |  |  |  |

|----|--------------|--------------------------------|--|--|--|--|--|

|    |              | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | TIMER0 module operation enable |  |  |  |  |  |

| 14 | TIMER0_CLKEN | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | PWM4 module operation enable   |  |  |  |  |  |

| 13 | PWM4_CLKEN   | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | PWM3 module operation enable   |  |  |  |  |  |

| 12 | PWM3_CLKEN   | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | PWM2 module operation enable   |  |  |  |  |  |

| 11 | PWM2_CLKEN   | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | PWM1 module operation enable   |  |  |  |  |  |

| 10 | PWM1_CLKEN   | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | PWM0 module operation enable   |  |  |  |  |  |

| 9  | 9 PWM0_CLKEN | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | IIC module operation enable    |  |  |  |  |  |

| 8  | IIC_CLKEN    | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | UART4 module operation enable  |  |  |  |  |  |

| 7  | UART4_CLKEN  | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | UART3 module operation enable  |  |  |  |  |  |

| 6  | UART3_CLKEN  | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | UART2 module operation enable  |  |  |  |  |  |

| 5  | UART2_CLKEN  | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | UART1 module operation enable  |  |  |  |  |  |

| 4  | UART1_CLKEN  | 1: Work                        |  |  |  |  |  |

|    | _            | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | UART0 module operation enable  |  |  |  |  |  |

| 3  | UART0_CLKEN  | 1: Work                        |  |  |  |  |  |

|    |              | 0: Off, the default is 0       |  |  |  |  |  |

|    |              | SPI1 module operation enable   |  |  |  |  |  |

| 2  | SPI1_CLKEN   | 1: Work                        |  |  |  |  |  |

| L  |              | 1. 1. 01K                      |  |  |  |  |  |

|   |            | 0: Off, the default is 0     |  |  |  |

|---|------------|------------------------------|--|--|--|

|   |            | SPI0 module operation enable |  |  |  |

| 1 | SPI0_CLKEN | 1: Work                      |  |  |  |

|   |            | 0: Off, the default is 0     |  |  |  |

| 0 | -          | Reserved                     |  |  |  |

#### **3.2.1.3.** System wake-up configuration register (WAKE\_CFG)

| Addre<br>Reset |          |    | -  | 7  |    |    |      |       |              |    |    |    |    |    |    |

|----------------|----------|----|----|----|----|----|------|-------|--------------|----|----|----|----|----|----|

| 31             | 30       | 29 | 28 | 27 | 26 | 25 | 24   | 23    | 22           | 21 | 20 | 19 | 18 | 17 | 16 |

|                |          |    |    |    |    |    | Rese | erved |              |    |    |    |    |    |    |

|                |          |    |    |    |    |    |      |       |              |    |    |    |    |    |    |

| 15             | 14       | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6            | 5  | 4  | 3  | 2  | 1  | 0  |

|                | Reserved |    |    |    |    |    |      |       | PLL_WAKE_TIM |    |    |    |    |    |    |

|                |          |    |    |    |    |    |      |       | RW           |    |    |    |    |    |    |

| 31:3 | -            | Reserved                |  |  |  |  |

|------|--------------|-------------------------|--|--|--|--|

|      |              | Wake up PLL timing time |  |  |  |  |

|      |              | 000: 0.2ms              |  |  |  |  |

|      |              | 001: 0.3ms              |  |  |  |  |

|      |              | 010: 0.4ms              |  |  |  |  |

| 2:0  | PLL_WAKE_TIM | 011: 0.5ms              |  |  |  |  |

|      |              | 100: 0.6ms              |  |  |  |  |

|      |              | 101: 0.7ms              |  |  |  |  |

|      |              | 110: 0.9ms              |  |  |  |  |

|      |              | 111: 1ms                |  |  |  |  |

# **3.2.2.** Hysteresis voltage selection of comparator in crystal oscillator register (XTAL\_HS\_SEL)

| Addres |             |    |    | 1  |        |     |      |       |    |    |    |    |    |        |       |

|--------|-------------|----|----|----|--------|-----|------|-------|----|----|----|----|----|--------|-------|

| 31     | 30          | 29 | 28 | 27 | 26     | 25  | 24   | 23    | 22 | 21 | 20 | 19 | 18 | 17     | 16    |

|        |             |    |    |    |        |     | Rese | erved |    |    |    |    |    |        |       |

|        |             |    |    |    |        |     |      |       |    |    |    |    |    |        |       |

|        |             |    |    |    |        | 15: | 2    |       |    |    |    |    |    | 1      | 0     |

|        |             |    |    |    |        |     |      |       |    |    |    |    | l  | HS_SEI | [1:0] |

|        | Reserved RW |    |    |    |        |     |      |       | 7  |    |    |    |    |        |       |

|        |             |    |    |    |        |     |      |       |    |    |    |    |    |        |       |

| 31:2   | -           |    |    |    | Reserv | red |      |       |    |    |    |    |    |        |       |

|     |             | Hysteresis voltage selection of comparator in crystal oscillator |

|-----|-------------|------------------------------------------------------------------|

|     |             | 00: 300mV                                                        |

| 1:0 | HS_SEL[1:0] | 01: 400mV                                                        |

|     |             | 10: 500mV                                                        |

|     |             | 11: 600mV                                                        |

## **3.2.3.** Analog module switch register (ANA\_CFG)

Address offset: 0x10

Reset value: 0x0000 0007

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23    | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|------|-------|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    | Rese | erved |    |    |    |    |    |    |    |

| 15:5     | 4            | 3        | 2       | 1      | 0      |

|----------|--------------|----------|---------|--------|--------|

|          | XTAL_HFR_SEL | XTAL_SEL | PD_XTAL | PD_CDC | PD_ADC |

| Reserved | RW           | RW       | RW      | RW     | RW     |

| 31:5 | -            | Reserved                                                               |  |  |  |  |  |

|------|--------------|------------------------------------------------------------------------|--|--|--|--|--|

|      |              | Analog high frequency crystal oscillator circuit selection             |  |  |  |  |  |

| 4    | XTAL_HFR_SEL | 0: 4MHz                                                                |  |  |  |  |  |

|      |              | 1: 8MHz                                                                |  |  |  |  |  |

|      |              | Frequency selection of analog crystal oscillator circuit               |  |  |  |  |  |

| 3    | XTAL_SEL     | 0: 32768Hz                                                             |  |  |  |  |  |

|      |              | 1: 4MHz/8MHz                                                           |  |  |  |  |  |

|      |              | Analog crystal oscillator circuit (32768Hz/4MHz/8MHz) control register |  |  |  |  |  |

| 2    | PD_XTAL      | 1: Off                                                                 |  |  |  |  |  |

|      |              | 0: On, off by default                                                  |  |  |  |  |  |

|      |              | CDC work control register                                              |  |  |  |  |  |

| 1    | PD_CDC       | 0: CDC module works normally                                           |  |  |  |  |  |

|      |              | 1: CDC module does not work                                            |  |  |  |  |  |

|      |              | Analog ADC shutdown control register                                   |  |  |  |  |  |

| 0    | PD_ADC       | 0: ADC module works normally                                           |  |  |  |  |  |

|      |              | 1: ADC module does not work                                            |  |  |  |  |  |

## 3.3. SysTick timer

#### 3.3.1. System timer description

SysTick timer, used to generate periodic interrupt requests. Features:

- 24-bit cyclic count down

- Automatic loading count initial value

- Configurable interrupts

- The count clock is the system clock

SysTick cannot wake up from standby mode.

SysTick is a 24-bit timer and counts down. After the timer count is reduced to 0, a programmable value will be reloaded and a SysTick exception will be generated at the same time. SysTick can be operated by polling or interruption. Programs that use polling can read the SysTick control and status registers and check COUNTFLAG. If the flag is set, it means that the SysTick count has been reduced to 0.

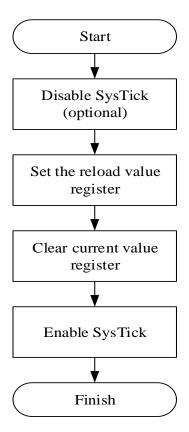

Directly operate register to control SysTick:

SysTick->CTRL = 0; // Disable SysTick SysTick->LOAD = 999; // Count down from 999 to 0 SysTick->VAL = 0; // Clear the current value to 0 SysTick->CTRL = 0x7; // Enable SysTick

The process of setting SysTick is as follows:

### 3.3.2. Registers

| Address    | Register | CMSIS symbol  | Description                         |

|------------|----------|---------------|-------------------------------------|

| 0xE000E010 | SYST_CSR | SysTick->CTRL | SysTick control and status register |

| 0xE000E014 | SYST_RVR | SysTick->LOAD | SysTick reload value register       |

| 0xE000E018 | SYST_CVR | SysTick->VAL  | SysTick current value register      |

### 3.3.2.1. SysTick control and status register (SYST\_CSR)

| Bit   | Bit symbol | Description                                                                                                                                                            | RW  | Reset value |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 31:17 | Reserved   | -                                                                                                                                                                      | -   | -           |

| 16    | COUNTFLAG  | <ul><li>SysTick timer overflow flag, read-only bit</li><li>1: Timer counts to 0</li><li>0: Timer did not count to 0</li><li>Reading register will be cleared</li></ul> | R   | 0           |

| 15:3  | Reserved   | -                                                                                                                                                                      | -   | -           |

| 2     | CLKSOURCE  | SysTick clock source<br>1: Use HCLK clock<br>0: Reserved                                                                                                               | R/W | 0           |

| 1     | TICKINT    | SysTick interrupt enable<br>1: Enable interrupt<br>0: Prohibit interrupt                                                                                               | R/W | 0           |

| 0     | ENABLE     | SysTick timer enable<br>1: Enable SysTick<br>0: Prohibit SysTick                                                                                                       | R/W | 0           |

#### 3.3.2.2. SysTick reload value register (SYST\_RVR)

| Bit   | Bit symbol | Description                           | RW  | Reset value |

|-------|------------|---------------------------------------|-----|-------------|

| 31:24 | Reserved   | -                                     | -   | -           |

| 23:0  | RELOAD     | Reload initial value of Systick timer | R/W | Undefined   |

#### 3.3.2.3. SysTick current value register (SYST\_CVR)

| Bit   | Bit symbol | Description                                                                                                                                                                       | RW  | Reset value |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 31:24 | Reserved   | -                                                                                                                                                                                 | -   | -           |

| 23:0  | CURRENT    | The current value of the Systick timer, writing<br>any value will clear the register, and<br>COUNTFLAG will also be cleared (does not<br>cause an exception to the Systick timer) | R/W | Undefined   |