# 1. BF7612CMXX MCU General Description

## 1.1. Features

- > Core: 1T 8051

- Operating frequency: 12MHz, 6MHz, 4MHz

- Clock error: ±1%@ 25°C, 5V

±3% @-40°C ~105°C, 5V

- > Memory

- CODE: 15K bytes

- $\circ$  DATA: 1K + 2\*512 bytes

- SRAM: 256 bytes(data)+512 bytes(xdata)

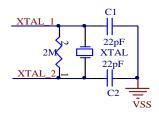

- Clock Source, Reset

- Internal low-speed clock LIRC: 32kHz Clock error: ±15%@25°C, 5V

- ±35% @-40°C ~105°C, 5V

- Internal high-speed RC oscillator: 1MHz

- External crystal oscillator: 32768Hz/4MHz

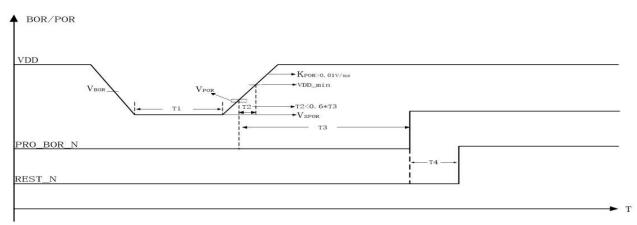

- $\circ$  7 resets, power-down reset voltage (Bor): 2.1V

- Low voltage detection: 2.4V/3.0V/3.6V/4.2V

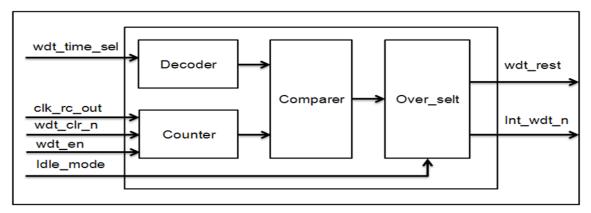

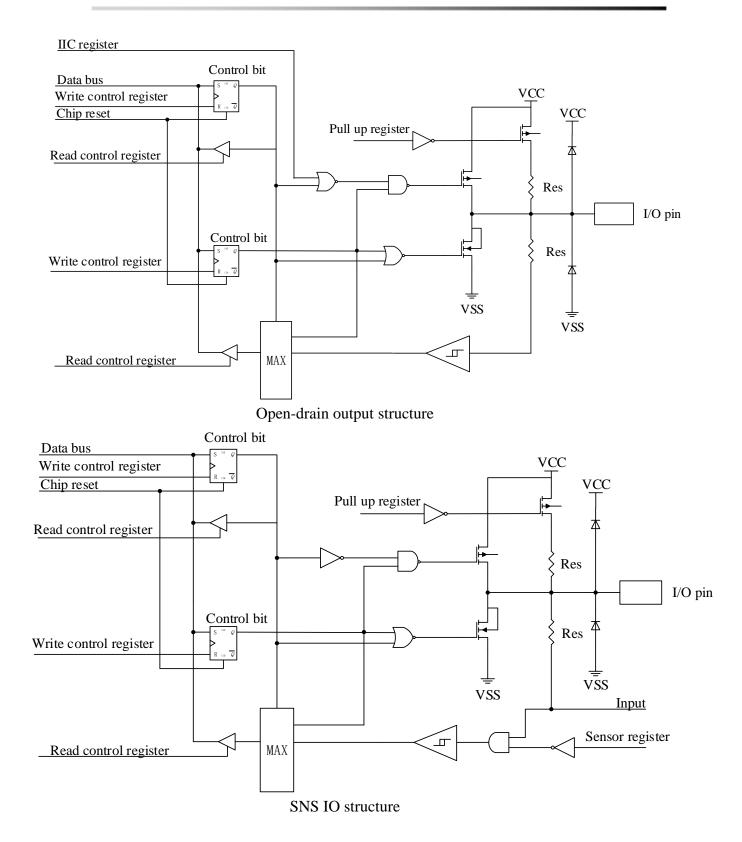

- > IO

- IO ports built-in pull-up resistor 4.7k

- High current sink port (PB0~PB7)

- $\circ \quad \text{Support IO function remapping} \\$

- INT0~2 (rising-edge, falling-edge, double edge)

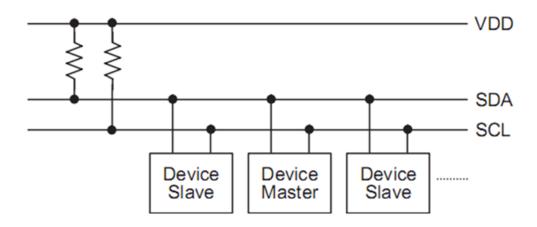

- Communication Module

- 2\*UART communication

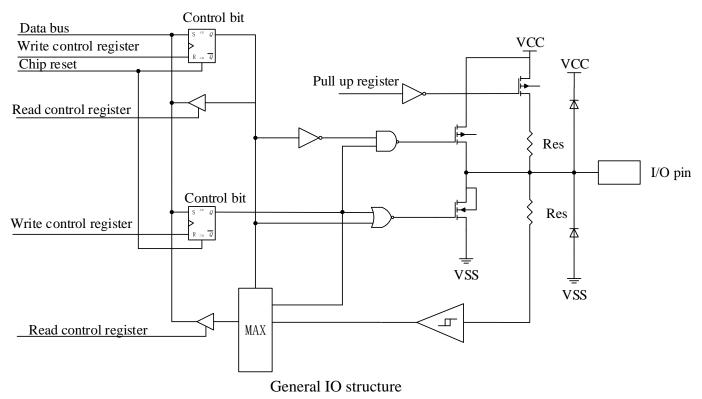

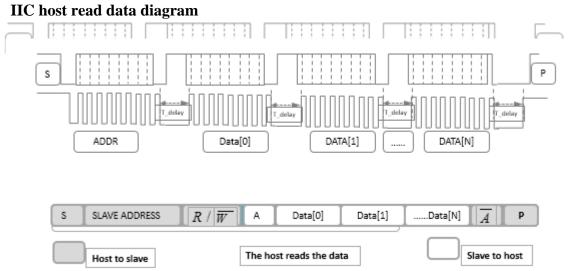

- $\circ$  IIC slave mode, support 100/400kHz

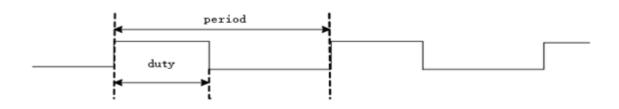

- > 16-bit PWM

- PWM0 supports 4 channels, with the same frequency, configurable duty cycle and polarity

- PWM1 supports 1 channel

- PWM2 supports 1 channel

- > Operating Voltage: 2.5 V ~ 5.5 V

- > Operating Temperature: -40 °C ~ 105 °C

- Enhanced industrial grade, in line with JESD industrial grade reliability certification standards

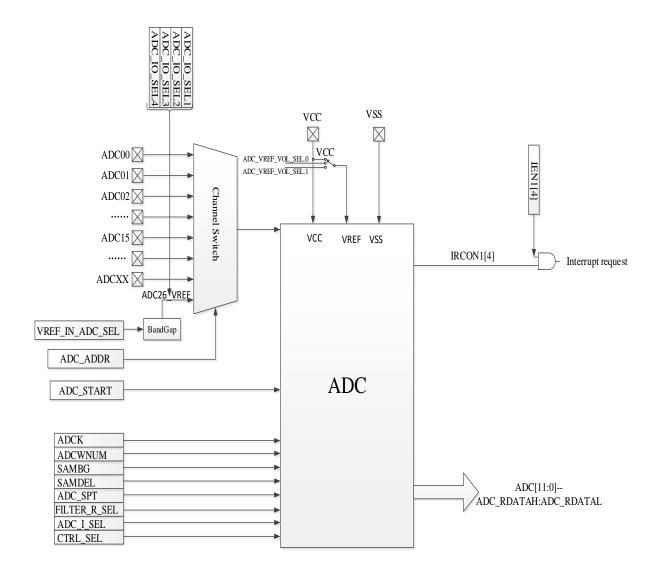

- > 12-bit High-speed ADC

- Up to 26 analog input channels

- Reference voltage: VCC

- > Interrupt

- Two-level interrupt priority capablity

- ADC, CSD, LED, INT0/1/2, LVDT, Timer0~2, WDT, UART0/1, IIC interrupt

- > Timer

- 16-bit Timer0/1, 32-bit Timer2

- Timer2 clock source: internal low-speed clock LIRC 32k or XTAL 32768Hz/4MHz

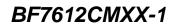

- Watchdog timer, overflow time 18ms to 2.304s

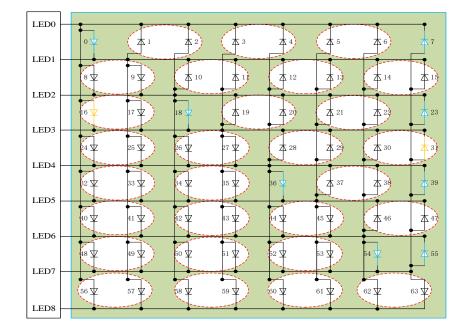

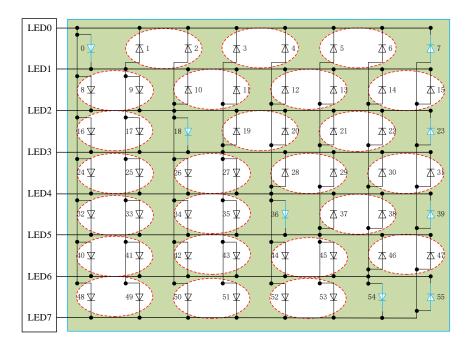

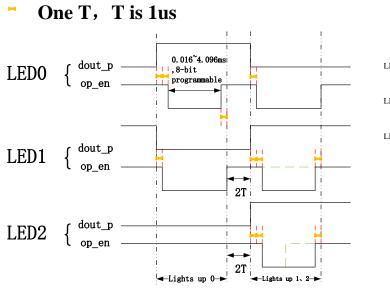

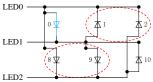

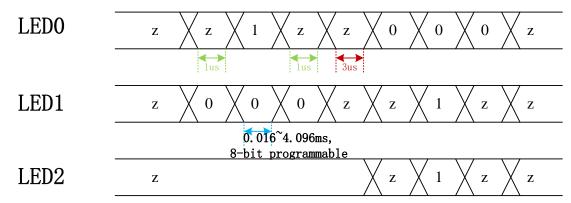

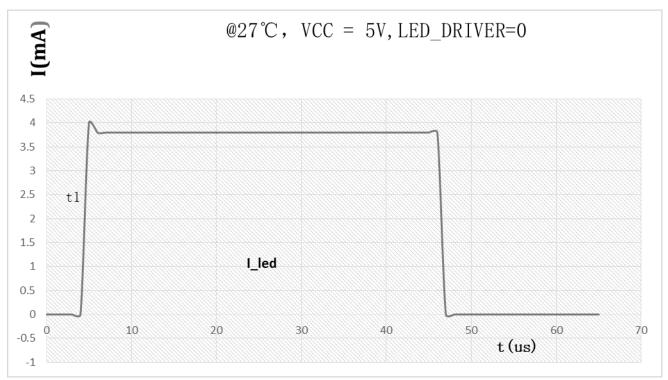

- LED Driver

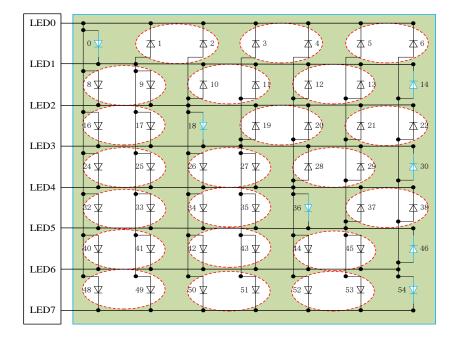

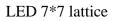

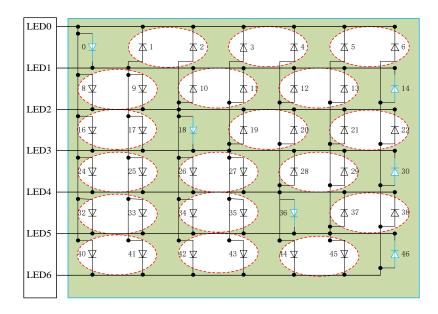

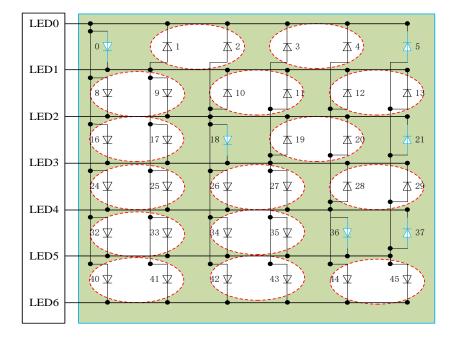

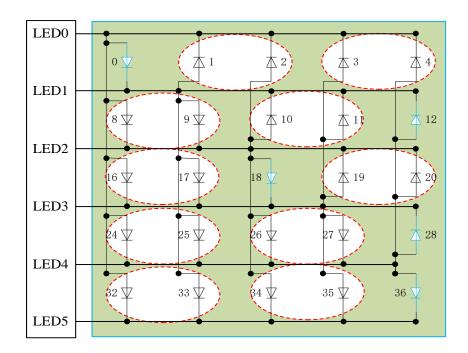

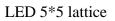

- 4x4, 5x5, 6x6, 6x7, 7x7, 7x8, 8x8 dot matrix driver

- Iow Power Management

- $\circ$  ~ Idle mode, power consumption 26  $\mu A$  @5V typical

- > CTK

- The key sensitivity is set independently

- Capacitive keys can be reused as GPIO

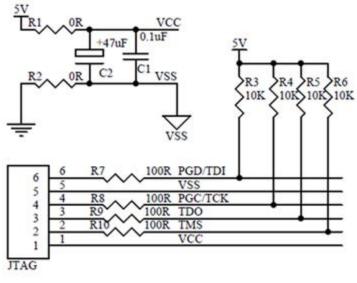

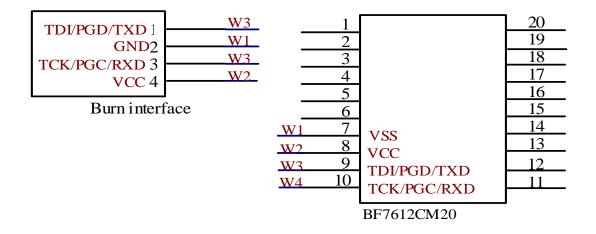

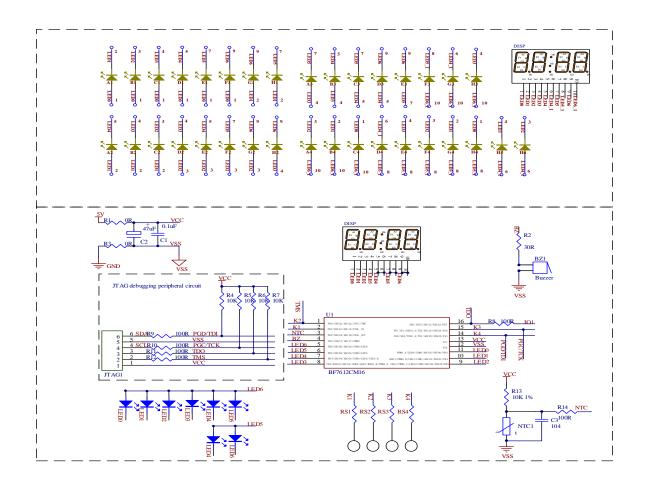

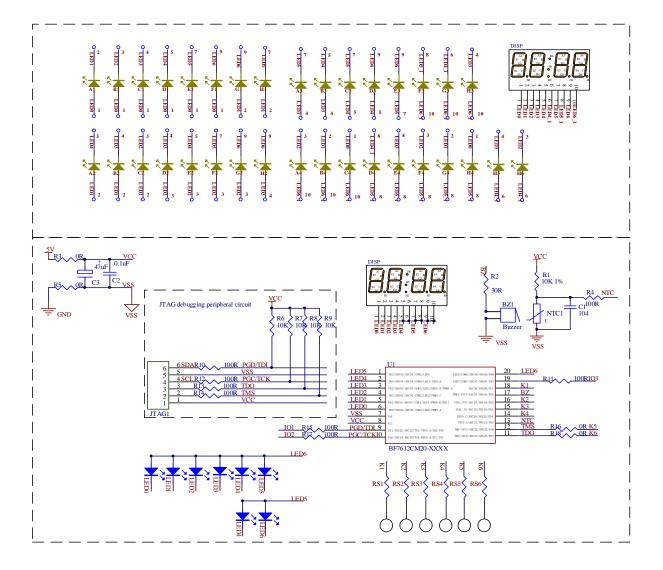

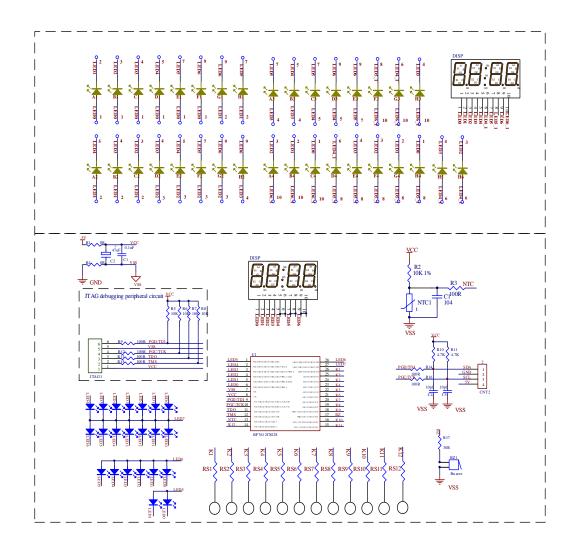

- > JTAG debug emulation interface

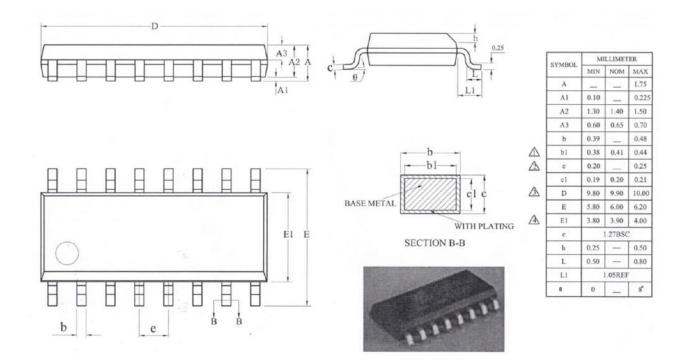

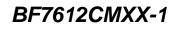

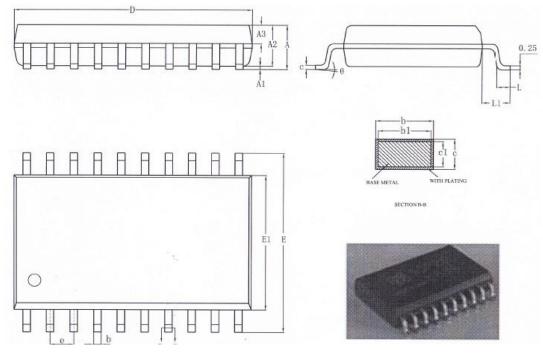

- Package

- SOP16/SOP20/SOP28

### **1.2. Overview**

The BF7612CMXX uses the high speed 8051 core with 1T instruction cycle, compared to the standard 8051 (12T) instruction cycle, it has the quicker running speed, compatibility standard 8051 instruction.

The BF7612CMXX includes a watchdog, key detection, LED serial dot matrix driver, IIC, UART, low voltage detection, power down reset, 16bit PWM, Timer0, Timer1, Timer2, 12bit successive approximation ADC, low power management, etc.

BF7612CMXX integrates multiple capacitive detection channels, which can be used for proximity sensing or touch detection. Each channel can be flexibly configured to achieve various applications such as buttons, wheels, sliders, etc., and each channel can adjust the touch sensitivity through the corresponding function register.

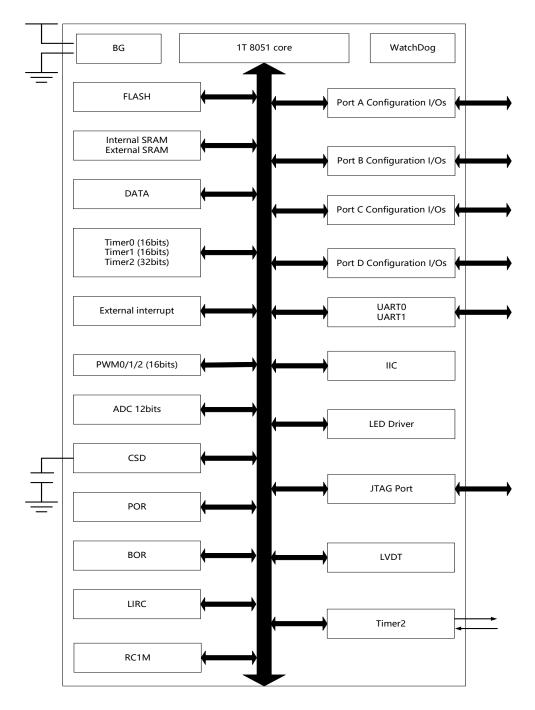

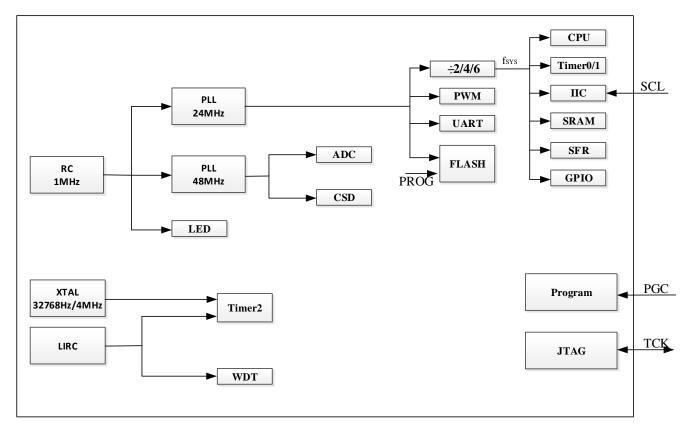

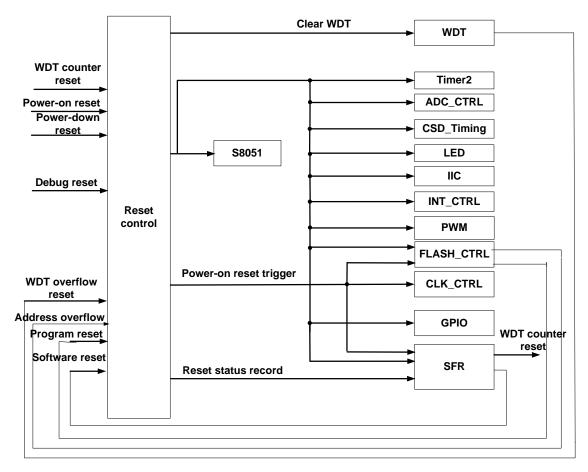

# **1.3. System Architecture**

System architecture

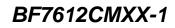

System bus frame diagram

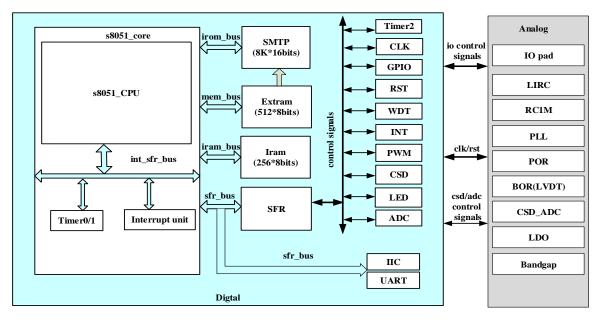

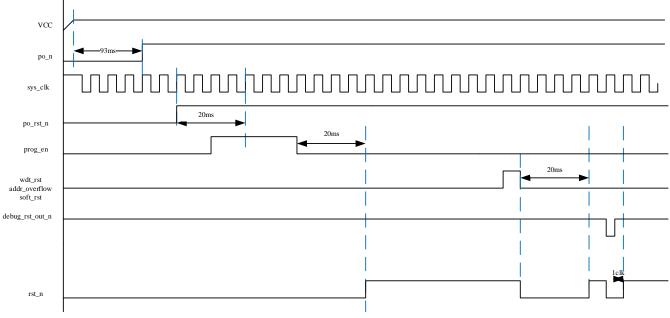

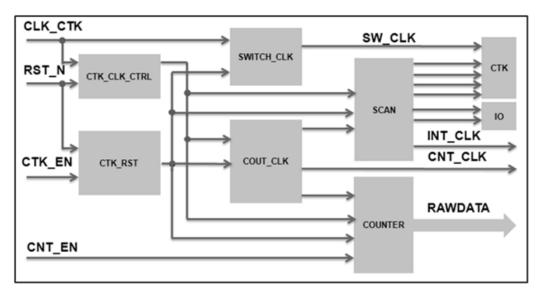

## 1.4. Clock Diagram

Clock diagram

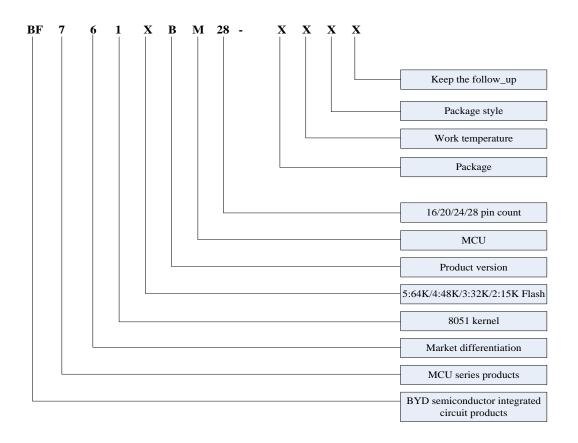

# **1.5. Selection List**

| T              | уре           | BF7612CM16<br>-SJLX | BF7612CM20-<br>SJLX | BF7612CM28<br>-SJLX |

|----------------|---------------|---------------------|---------------------|---------------------|

| Operating      | Voltage (V)   | 2.5~5.5             | 2.5~5.5             | 2.5~5.5             |

| Operating fr   | requency (Hz) | 12M                 | 12M                 | 12M                 |

| C              | ore           | 1T 8051             | 1T 8051             | 1T 8051             |

|                | CODE          | 15K                 | 15K                 | 15K                 |

| Memory(Bytes)  | DATA          | 1K + 2*512          | 1K + 2*512          | 1K + 2*512          |

|                | SRAM          | 256+512             | 256+512             | 256+512             |

|                | WDT           | 1                   | 1                   | 1                   |

| <b>T</b> '     | Timer0 *16bit | 1                   | 1                   | 1                   |

| Timer          | Timer1 *16bit | 1                   | 1                   | 1                   |

|                | Timer2 *32bit | 1                   | 1                   | 1                   |

| Communication  | IIC           | 1                   | 1                   | 1                   |

| module         | UART          | 2                   | 2                   | 2                   |

| G              | PIO           | 14                  | 18                  | 26                  |

| K              | EY            | 14                  | 18                  | 26                  |

| Ι              | NT            | 2                   | 3                   | 3                   |

| C              | ОМ            | 7                   | 8                   | 8                   |

| Analog module  | ADC*12bit     | 14                  | 18                  | 26                  |

| Display module | LED serial    | 6*7                 | 7*8                 | 8*8                 |

|                | PWM0 *16bit   | 4                   | 4                   | 4                   |

| PWM module     | PWM1 *16bit   | -                   | 1                   | 1                   |

|                | PWM2 *16bit   | 1                   | -                   | 1                   |

| Pac            | kage          | SOP16(9.9*3.9mm)    | SOP20(12.8*7.5mm)   | SOP28(18*7.5mm)     |

Selection list

### 1.6. Pin Assignment

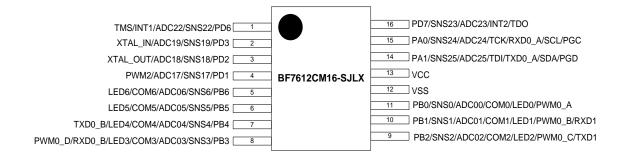

### 1.6.1. BF7612CM16-SJLX

SOP16 package pin diagram

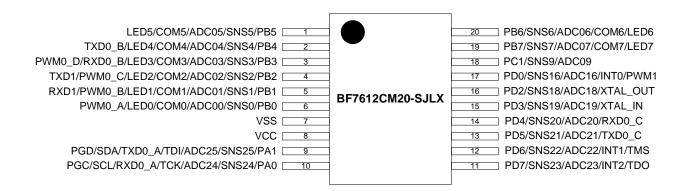

## 1.6.2. BF7612CM20-SJLX

SOP20 package pin diagram

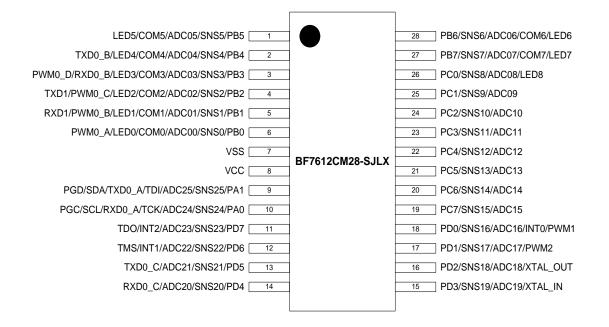

### 1.6.3. BF7612CM28-SJLX

Note: The SNS24 and SNS25 touch channels are multiplexed with debug programming pins. Generally, it is not recommended to use them as touch channels.

# **1.7. Pin Description**

| BF7612CM28-SJLX | BF7612CM20-SJLX | BF7612CM16-SJLX | Function description                                                                                                                                                                                                             |

|-----------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 1               | 6               | Default function: GPIO <pb5><br/>Other function: SNSXX: Touch key channel<br/>ADCXX: ADC channel<br/>COMX: Large current sink<br/>LEDX: LED serial dot matrix</pb5>                                                              |

| 2               | 2               | 7               | Default function: GPIO <pb4><br/>Other function: SNSXX: Touch key channel<br/>ADCXX: ADC channel<br/>COMX: Large current sink<br/>LEDX: LED serial dot matrix<br/>TXDXX: serial pot transmission</pb4>                           |

| 3               | 3               | 8               | Default function: GPIO <pb3><br/>Other function: SNSXX: Touch key channel<br/>ADCXX: ADC channel<br/>COMX: Large current sink<br/>LEDX: LED serial dot matrix<br/>RXDXX: serial pot reception<br/>PWMXX: PWM output port</pb3>   |

| 4               | 4               | 9               | Default function: GPIO <pb2><br/>Other function: SNSXX: Touch key channel<br/>ADCXX: ADCchannel<br/>COMX: Large current sink<br/>LEDX: LED serial dot matrix<br/>PWMXX: PWM output port<br/>TXDXX: serial pot transmission</pb2> |

| 5               | 5               | 10              | Default function: GPIO <pb1><br/>Other function: SNSXX: Touch key channel<br/>ADCXX: ADC channel<br/>COMX: Large current sink<br/>LEDX: LED serial dot matrix<br/>PWMXX: PWM output port<br/>RXDXX: serial pot reception</pb1>   |

|    |    |    | Default function: GPIO <pb0></pb0>          |

|----|----|----|---------------------------------------------|

|    |    |    | Other function: SNSXX: Touch key channel    |

| 6  | 6  | 11 | ADCXX: ADC channel                          |

|    |    |    | COMX: Large current sink                    |

|    |    |    | LEDX: LED serial dot matrix                 |

|    |    |    | PWMXX: PWM output port                      |

| 7  | 7  | 12 | Default function: GND <vss></vss>           |

| 8  | 8  | 13 | Default function: Power supply <vcc></vcc>  |

|    |    |    | Default function: GPIO <pa1></pa1>          |

|    |    |    | Other function: SNSXX: Touch key channel    |

|    |    |    | ADCXX: ADC channel                          |

| 9  | 9  | 14 | TDI: JTAG emulation test data serial input  |

|    |    |    | TXDXX: serial pot transmission              |

|    |    |    | SDAXX: IIC serial data line                 |

|    |    |    | PGD: Burning port PGD                       |

|    |    |    | Default function: GPIO <pa0></pa0>          |

|    |    |    | Other function: SNSXX: Touch key channel    |

|    |    |    | ADCXX: ADC channel                          |

| 10 | 10 | 15 | TCK: JTAG simulation test clock             |

|    |    |    | RXDXX: serial pot reception                 |

|    |    |    | SCLXX: Serial clock line of IIC             |

|    |    |    | PGC: Burning port PGC                       |

|    |    |    | Default function: GPIO <pd7></pd7>          |

|    |    |    | Other function: SNSXX: Touch key channel    |

| 11 | 11 | 16 | ADCXX: ADC channel                          |

|    |    |    | INTXX: External Interrupt                   |

|    |    |    | TDO: JTAG emulation test data serial output |

|    |    |    | Default function: GPIO <pd6></pd6>          |

|    |    |    | Other function: SNSXX: Touch key channel    |

| 12 | 12 | 1  | ADCXX: ADC channel                          |

|    |    |    | INTXX: External Interrupt                   |

|    |    |    | TMS: JTAG simulation test mode selection    |

|    |    |    | Default function: GPIO <pd5></pd5>          |

| 13 | 13 |    | Other function: SNSXX: Touch key channel    |

| 15 | 15 | -  | ADCXX: ADC channel                          |

|    |    |    | TXDXX: serial pot transmission              |

|    |    |    | Default function: GPIO <pd4></pd4>          |

| 14 | 14 |    | Other function: SNSXX: Touch key channel    |

| 14 | 14 | -  | ADCXX: ADC channel                          |

|    |    |    | RXDXX: serial pot reception                 |

| 15 | 15 | 2  | Default function: GPIO <pd3></pd3>          |

|    |    |   | 0.1 5               |                                   |

|----|----|---|---------------------|-----------------------------------|

|    |    |   |                     | SNSXX: Touch key channel          |

|    |    |   |                     | ADCXX: ADC channel                |

|    |    |   |                     | TAL0_IN: External crystal input   |

|    |    |   | Default function: ( |                                   |

| 16 | 16 | 3 |                     | SNSXX: Touch key channel          |

|    |    | - |                     | ADCXX: ADC channel                |

|    |    |   | Σχ                  | TAL0_OUT: External crystal output |

|    |    |   | Default function: C |                                   |

| 17 | _  | 4 |                     | SNSXX: Touch key channel          |

| 17 |    | • | A                   | ADCXX: ADC channel                |

|    |    |   | P                   | PWMXX: PWM output port            |

|    |    |   | Default function: C |                                   |

|    |    |   | Other function: S   | SNSXX: Touch key channel          |

| 18 | 17 | - | A                   | ADCXX: ADC channel                |

|    |    |   | Ι                   | NTXX: External Interrupt          |

|    |    |   | P                   | WMXX: PWM output port             |

|    |    |   | Default function: C | GPIO <pc7></pc7>                  |

| 19 | -  | - | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: O | GPIO <pc6></pc6>                  |

| 20 | -  | - | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: ( | GPIO <pc5></pc5>                  |

| 21 | -  | - | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: ( | GPIO <pc4></pc4>                  |

| 22 | -  |   | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: O | GPIO <pc3></pc3>                  |

| 23 | -  |   | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: O | GPIO <pc2></pc2>                  |

| 24 | -  | - | Other function: S   | SNSXX: Touch key channel          |

|    |    |   |                     | ADCXX: ADC channel                |

|    |    |   | Default function: C | GPIO <pc1></pc1>                  |

| 25 | 18 | - | Other function: S   | SNSXX: Touch key channel          |

|    |    |   | A                   | ADCXX: ADC channel                |

|    |    |   | Default function: C | GPIO <pc0></pc0>                  |

|    |    |   | Other function: S   | SNSXX: Touch key channel          |

| 26 | -  | - |                     | ADCXX: ADC channel                |

|    |    |   |                     | EDX: LED serial dot matrix        |

|    |    |   |                     | EDA: LED serial dot mainx         |

|    |    |   | Default function: GPIO <pb7></pb7>       |

|----|----|---|------------------------------------------|

|    |    |   | Other function: SNSXX: Touch key channel |

| 27 | 19 | - | ADCXX: ADC channel                       |

|    |    |   | COMX: Large current sink                 |

|    |    |   | LEDX: LED serial dot matrix              |

|    |    |   | Default function: GPIO <pb6></pb6>       |

|    |    |   | Other function: SNSXX: Touch key channel |

| 28 | 20 | 5 | ADCXX: ADC channel                       |

|    |    |   | COMX: Large current sink                 |

|    |    |   | LEDX: LED serial dot matrix              |

Package pin correspondence diagram

# 2. Electrical Characteristic

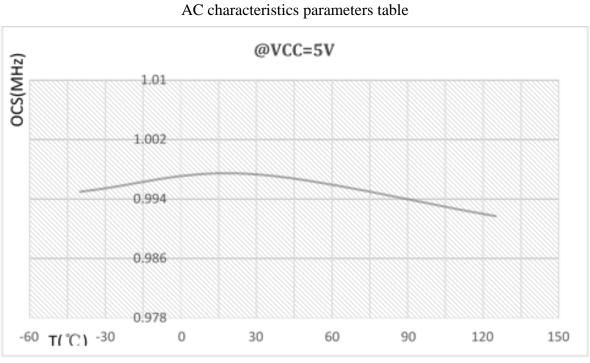

## **2.1. AC Characteristics**

| D                 | Course had          | Cor       | Conditions   |      | Trm    | May  | TI   |

|-------------------|---------------------|-----------|--------------|------|--------|------|------|

| Parameter         | Symbol              | VCC       | Temperature  | Min  | Тур    | Max  | Unit |

| C.                | Internal high-speed | 51/       | -20°C~65°C   | -1%  | 1      | +1%  | MII- |

| f <sub>RC1M</sub> | RC oscillator       | 5V        | -40°C ~105°C | -3%  | 1      | +3%  | MHz  |

| C                 | System clock        | 5V        | -20°C~65°C   | -1%  | 12/6/4 | +1%  | MIT  |

| f <sub>SYS</sub>  |                     |           | -40°C ~105°C | -3%  | 12/6/4 | +3%  | MHz  |

|                   | Internal low-speed  | <b>CN</b> | 25°C         | -15% | 32     | +15% | 1.11 |

| f <sub>LIRC</sub> | RC oscillator       | 5V        | -40°C ~105°C | -35% | 32     | +35% | kHz  |

### RC1M (OSC) temperature characteristic curve

# **2.2. DC Characteristics**

|                   |                                                                     |          |                                                                                 |         |     | Та      | =25°C |

|-------------------|---------------------------------------------------------------------|----------|---------------------------------------------------------------------------------|---------|-----|---------|-------|

| Parameter         | Symbol                                                              | ,        | Test Conditions                                                                 | Min     | Тур | Max     | Unit  |

|                   | Symbol                                                              | VCC      | Conditions                                                                      |         | тур | Max     | Umt   |

| VCC               | Operating<br>Voltage                                                | -        | -                                                                               | 2.5     | -   |         | V     |

|                   |                                                                     | 3.3V     | f <sub>SYS</sub> =12 MHz, no load,                                              | -       | 2.0 | 2.6     |       |

|                   |                                                                     | 5V       | all peripherals off                                                             | -       | 2.1 | 2.7     |       |

| т                 | Active mode                                                         | 3.3V     | f <sub>SYS</sub> =6 MHz, no load, all                                           | -       | 1.6 | 2.0     |       |

| I <sub>OP</sub>   | current                                                             | 5V       | peripherals off                                                                 | -       | 1.7 | 2.2     | mA    |

|                   |                                                                     | 3.3V     | f <sub>SYS</sub> =4 MHz, no load, all                                           | -       | 1.4 | 1.8     |       |

|                   |                                                                     | 5V       | peripherals off                                                                 | -       | 1.5 | 2.0     |       |

| т                 | idle mode                                                           | 3.3V     | PCON = 0x01, all                                                                | -       | 27  | 36      |       |

| I <sub>STB0</sub> | current                                                             | 5V       | peripherals off                                                                 | -       | 26  | 35      | μA    |

|                   |                                                                     | 3.3V     | WDT_CTRL=7, WDT<br>interrupt 2s wake up,<br>2ms working time, IO                | -       | 28  | 39      |       |

|                   | Average<br>current for<br>intermittent<br>wake-up from<br>idle mode | 5V       | output is low, close other functions                                            | -       | 29  | 38      | μA    |

|                   |                                                                     | 3.3V     | Timer2 external crystal<br>oscillator wakes up in                               | -       | 28  | 39      |       |

| I <sub>stb1</sub> |                                                                     | 5V       | 2s, 2ms working time,<br>IO output is low, and<br>other functions are<br>closed | -       | 29  | 38      | μΑ    |

|                   |                                                                     | 3.3V     | CSD parallel mode,<br>WDT interrupt 2s wake-                                    | -       | 28  | 39      |       |

|                   |                                                                     | 5V       | up, 2ms working time,<br>IO output low, close<br>other functions                | -       | 29  | 38      | μA    |

| V <sub>IL</sub>   | Input low level                                                     | 2.5~5.5V | -                                                                               | -       | -   | 0.3*VCC | V     |

| V <sub>IH</sub>   | Input high<br>level                                                 | 2.5~5.5V | -                                                                               | 0.7*VCC | -   | -       | V     |

| V <sub>INTL</sub> | INT input low<br>level                                              | 2.5~5.5V | -                                                                               | -       | -   | 0.3*VCC | v     |

| V <sub>INTH</sub> | INT input high<br>level                                             | 2.5~5.5V | -                                                                               | 0.7*VCC | -   | -       | V     |

| V <sub>OL</sub>   | output low<br>voltage                                               | 5V       | I <sub>OL</sub> =60mA                                                           | -       | -   | 0.1*VCC | V     |

| V <sub>OH</sub>   | output high voltage      | 5V | I <sub>OH</sub> =16mA   | 0.9*VCC | -   | - | v  |

|-------------------|--------------------------|----|-------------------------|---------|-----|---|----|

| Iol               | IO sink current          | 5V | V <sub>OL</sub> =0.1VCC | -       | 60  | - | mA |

| I <sub>OH</sub>   | IO Source<br>current     | 5V | V <sub>OH</sub> =0.9VCC | -       | 17  | - | mA |

| I <sub>COM</sub>  | PB large sink<br>current | 5V | V <sub>OL</sub> =0.1VCC | -       | 120 | - | mA |

| I <sub>Leak</sub> | Input leakage current    | 5V | -                       | -       | 1   | 5 | μΑ |

| R <sub>PH</sub>   | IO internal<br>pull-up   | 5V | -                       | -       | 4.7 | - | kΩ |

# **2.3. ADC Characteristics**

|                   |                                 |     |                 | -     | -         |                  | Ta=25°C |

|-------------------|---------------------------------|-----|-----------------|-------|-----------|------------------|---------|

| Parameter         | Symbol                          |     | Test Conditions | Min   | Тур       | N/               | Unit    |

| Parameter         | Symbol                          | VCC | Conditions      |       | тур       | Max              | Umt     |

| V <sub>ADC</sub>  | Supply Voltage                  | -   | -               | 2.5   | -         | 5.5              | V       |

| N <sub>R</sub>    | Accuracy                        | -   | -               | -     | 9         | 10               | Bit     |

| V <sub>ADCI</sub> | ADC Input voltage               | -   | -               | VSS   |           | $V_{\text{REF}}$ | V       |

| I <sub>ADCI</sub> | input current                   | -   | -               | -     | -         | 1                | μΑ      |

| DNL               | Differential nonlinear<br>error | 5V  | -               | -     | <u>+4</u> | ±6               | LSB     |

| INL               | Integral nonlinear error        | 5V  | -               | -     | ±4        | ±6               | LSB     |

| t1                | ADC sampling time               | -   | -               | 0.5   | -         | -                | μs      |

| t <sub>ADC</sub>  | ADC conversion time             | -   | -               | 2.625 | -         | -                | μs      |

| RESO              | Resolution                      | -   | -               |       | 12        |                  | Bit     |

| N <sub>ADC</sub>  | Input channel                   | -   | -               | -     | -         | 26               | Channel |

ADC characteristic parameter table

# 2.4. Limit Parameters

| D                | Course had                           | Test | Conditions | Min     | Тур  | Max     | T    |

|------------------|--------------------------------------|------|------------|---------|------|---------|------|

| Parameter        | Symbol                               | VCC  | Conditions | 191111  | тур  | IVIAX   | Unit |

| VCC              | Supply voltage when working          | -    | -          | VSS+2.5 | -    | VSS+5.5 | V    |

| T <sub>STG</sub> | Non-working storage temperature      | -    | -          | -40     | -    | 125     | °C   |

| Та               | Operating temperature                | -    | -          | -40     | -    | 105     | °C   |

| Vin              | I/O input voltage                    | -    | -          | VSS-0.5 | -    | VCC+0.5 | V    |

| I <sub>OLA</sub> | IOL total current                    | -    | -          |         | 130  |         | mA   |

| I <sub>OHA</sub> | IOH total current                    | -    | -          |         | -130 |         | mA   |

| ESD(HBM)         | Port electrostatic discharge voltage | -    | -          | -8      | -    | 8       | kV   |

Limit parameters characteristics parameters table

Notes: Exceed the limit parameters may cause damage to the chip, unable to expect the chip work outside the above indicated range. If you work under conditions outside the marked range for a long time, it may affect the reliability of the chip.

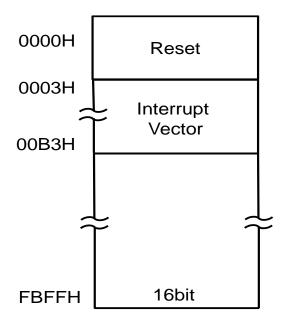

## 3. Memory and SFR

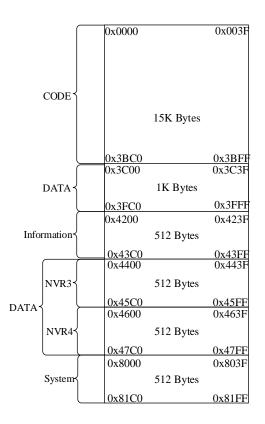

### 3.1. Flash

FLASH features are as follows:

- CODE area: ICP programming supports block erase, page erase, byte write

- DATA area: page erase, byte write

- Program/erase times: CODE area: at least 20000 times @25°C

DATA area: at least 20000 times @25°C

Data storage period: 100 Years@25°C 20 Years@85°C

Flash Storage Architecture

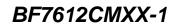

| Module      | Address range       | Space size (Bytes) | Page |

|-------------|---------------------|--------------------|------|

| CODE        | 0x0000~0x3BFF       | 15K                | 30   |

|             | 0x3C00~0x3FFF       | 1K                 | 1    |

| DATA        | NVR3: 0x4400~0x45FF | 512                | 1    |

|             | NVR4: 0x4600~0x47FF | 512                | 1    |

| Information | 0x4200~0x43FF       | 512                | 1    |

| System      | 0x8000~0x81FF       | 512                | 1    |

Steps to read the unique identification code (UID) of the chip:

- 1. Turn off the interrupt;

- 2. The read CODE absolute address 0x43A8~0x43AF corresponds to product ID1~ID8.

- 3. Restore interrupt settings.

#### Note:

- **1.** It is recommended that BOR must be turned on at the first initialization of the program to reduce the risk of errors.

- 2. It is not recommended to store the DATA area (0x3C00~0x3FFF) as the user CODE.

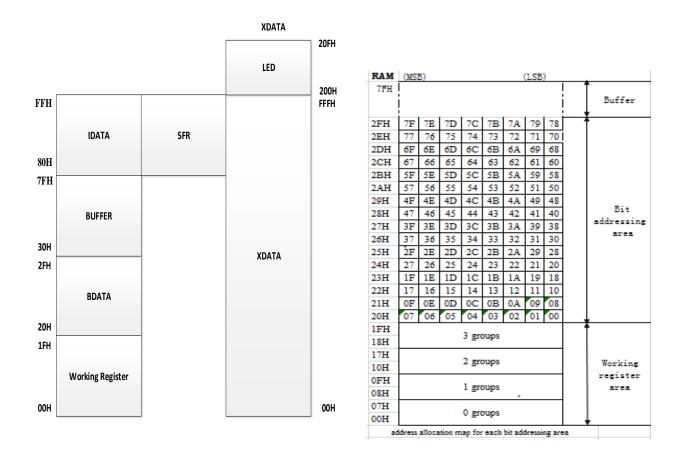

## 3.2. RAM

There are 256 Bytes inside, with addresses ranging from 00H to FFH. These include the working register group, bit-addressing area, buffer, and SFR, where the buffer contains the stack area.

Internal low 128 Bytes: a total of 128 Bytes from 00H to 7FH. Data can be read and written in either immediate or indirect addressing mode.

Internal high 128 Bytes: a total of 128 Bytes from 80H to FFH. Data can only be read and written through the working register indirect addressing mode.

Special function register SFR: Address is 80H~FFH, can only read and write data by direct addressing.

Xdata contains 512 Bytes. The address ranges from 0000H to 01FFH. Users can use this area completely. Data is read and written by means of data pointers or working register addressing.

LED storage RAM occupies XRAM bus, Address is 200~20FH. This area is the LED display cache, and the display content can be modified by changing the data in this area.

When writing programs, pay attention to reserving stack space to avoid the program running out of stack overflow. In C programming, the stack header is automatically assigned by the program, but must be stored in data or IDATA. The start address of the stack can be set in startup. A51 in Keil.

RAM address space allocation diagram:

| The following table  | lists the methods to a | pet value in the thr | e parts of RAM: |

|----------------------|------------------------|----------------------|-----------------|

| The following tuble. | mous the methods to g  | Set value in the th  |                 |

|       | MOV     | A,direct        |

|-------|---------|-----------------|

|       | MOV     | direct,A        |

| DATA  | MOV     | direct,#data    |

| DATA  | MOV     | direct1,direct2 |

|       | MOV     | Rn,direct       |

|       | MOV     | direct,Rn       |

|       | MOV     | A,@Ri           |

|       | MOV     | @Ri,A           |

| IDATA | MOV     | direct,@Ri      |

|       | MOV     | @Ri,direct      |

|       | MOV     | @Ri,#data       |

| XDATA | MOVX @I | DPTR,A          |

| ADATA | MOVX A, | @DPTR           |

RAM value instruction table

In the above table, n ranges from 0 to 7, and i ranges from 0 to 1.

## 3.3. SFR Table

| Address | Name          | W/R | Reset | Function description                              |  |  |

|---------|---------------|-----|-------|---------------------------------------------------|--|--|

| 0x80    | DATAB         | RW  | 0xFF  | PB data register                                  |  |  |

| 0x81    | SP            | RW  | 0x07  | Stack pointer register                            |  |  |

| 0x82    | DPL           | RW  | 0x00  | Data pointer register0 low 8-bit                  |  |  |

| 0x83    | DPH           | RW  | 0x00  | Data pointer register0 high 8-bit                 |  |  |

| 0x84    | SYS_CLK_CFG   | RW  | 0x01  | Clock control register                            |  |  |

| 0x85    | INT_PE_STAT   | RW  | 0x00  | WDT/Timer2 interrupt status register              |  |  |

| 0x86    | INT_POBO_STAT | RW  | 0x00  | LVDT boost/LVDT buck interrupt status register    |  |  |

| 0x87    | PCON          | RW  | 0x00  | Idle mode selection register                      |  |  |

| 0x88    | TCON          | RW  | 0x05  | Timer control register                            |  |  |

| 0x89    | TMOD          | RW  | 0x00  | Timer mode register                               |  |  |

| 0x8A    | TL0           | RW  | 0x00  | Timer 0 counter low 8-bit                         |  |  |

| 0x8B    | TL1           | RW  | 0x00  | Timer 1 counter low 8-bit                         |  |  |

| 0x8C    | TH0           | RW  | 0x00  | Timer 0 counter high 8-bit                        |  |  |

| 0x8D    | TH1           | RW  | 0x00  | Timer 1 counter high 8-bit                        |  |  |

| 0x8E    | SOFT_RST      | RW  | 0x00  | Soft reset register                               |  |  |

| 0x90    | DATAC         | RW  | 0xFF  | PC port data register                             |  |  |

| 0x91    | WDT_CTRL      | RW  | 0x00  | WDT timing overflow control register              |  |  |

| 0x92    | WDT_EN        | RW  | 0x00  | WDT timing enable register                        |  |  |

| 0x93    | TIMER2_CFG    | RW  | 0x00  | TIMER2 CFG register                               |  |  |

| 0x94    | TIMED2 SET H  | RW  | 000   | TIMER2 count value configuration register, high 8 |  |  |

| 0x94    | TIMER2_SET_H  | ĸw  | 0x00  | bits                                              |  |  |

| 0x95    | TIMED2 SET I  | RW  | 0x00  | TIMER2 count value configuration register, low 8  |  |  |

| 0.000   | TIMER2_SET_L  | ĸw  | 0x00  | bits                                              |  |  |

| 0x96    | REG_ADDR      | RW  | 0x00  | Second address bus register                       |  |  |

| 0x97    | REG_DATA      | RW  | 0x00  | Second data read and write bus register           |  |  |

| 0x98    | DATAD         | RW  | 0xFF  | PD port data register                             |  |  |

| 0x99    | PWM1_L_L      | RW  | 0x00  | PWM1 low level control register(low 8-bit)        |  |  |

| 0x9A    | PWM1_L_H      | RW  | 0x00  | PWM1 low level control register(high 8-bit)       |  |  |

| 0x9B    | PWM1_H_L      | RW  | 0x00  | PWM1 high level control register(low 8-bit)       |  |  |

| 0x9C    | PWM1_H_H      | RW  | 0x00  | PWM1 high level control register(high 8-bit)      |  |  |

| 0x9D    | PWM2_L_L      | RW  | 0x00  | PWM2 low level control register(low 8-bit)        |  |  |

| 0x9E    | PWM2_L_H      | RW  | 0x00  | PWM2 low level control register(high 8-bit)       |  |  |

| 0x9F    | PWM2_H_L      | RW  | 0x00  | PWM2 high level control register(low 8-bit)       |  |  |

| 0xA0    | P2_XH         | RW  | 0xFF  | MOVX @Ri,A operation xdata address high 8 bits    |  |  |

| 0xA1    | PWM2_H_H      | RW  | 0x00  | PWM2 high level control register(high 8-bit)      |  |  |

| 0xA2    | PWM_EN        | RW  | 0x00  | PWM control register                              |  |  |

| 0xA3    | PWM0_CH_CTRL  | RW  | 0x00  | PWM0 control register                             |  |  |

# BF7612CMXX-1

| 0xA4 | PWM0_CH0_CNT_L | RW | 0x00 | PWM0 channel 0 count value configuration register low 8 bits     |  |  |  |

|------|----------------|----|------|------------------------------------------------------------------|--|--|--|

| 0xA5 | PWM0_CH0_CNT_H | RW | 0x00 | PWM0 channel 0 count value configuration register<br>high 8 bits |  |  |  |

| 0xA6 | PWM0_CH1_CNT_L | RW | 0x00 | PWM0 channel 1 count value configuration register<br>low 8 bits  |  |  |  |

| 0xA7 | PWM0_CH1_CNT_H | RW | 0x00 | PWM0 channel 1 count value configuration registe                 |  |  |  |

| 0xA8 | IEN0           | RW | 0x00 | Interrupt enable register                                        |  |  |  |

| 0xA9 | PWM0_CH2_CNT_L | RW | 0x00 | PWM0 channel 2 count value configuration registe<br>low 8 bits   |  |  |  |

| 0xAA | PWM0_CH2_CNT_H | RW | 0x00 | PWM0 channel 2 count value configuration register<br>high 8 bits |  |  |  |

| 0xAB | PWM0_CH3_CNT_L | RW | 0x00 | PWM0 channel 3 count value configuration register<br>low 8 bits  |  |  |  |

| 0xAC | PWM0_CH3_CNT_H | RW | 0x00 | PWM0 channel 3 count value configuration register<br>high 8 bits |  |  |  |

| 0xAD | PWM0_MOD_L     | RW | 0x00 | PWM0 cycle configuration register low 8 bits                     |  |  |  |

| 0xAE | PWM0_MOD_H     | RW | 0x00 | PWM0 cycle configuration register high 8 bits                    |  |  |  |

| 0xAF | SCAN_START     | RW | 0x00 | LED scan open register                                           |  |  |  |

| 0xB0 | DP_CON         | RW | 0x00 | LED scan control register                                        |  |  |  |

| 0xB1 | SCAN_WIDTH     | RW | 0x00 | LED scan on time 1 control register                              |  |  |  |

| 0xB2 | LED2_WIDTH     | RW | 0x00 | LED scan on time 2 control register                              |  |  |  |

| 0xB3 | LED_DRIVE      | RW | 0x00 | LED drive capability configuration register                      |  |  |  |

| 0xB4 | ADC_SPT        | RW | 0x00 | ADC sample time configure register                               |  |  |  |

| 0xB5 | ADC_SCAN_CFG   | RW | 0x00 | ADC scan control register                                        |  |  |  |

| 0xB6 | ADCCKC         | RW | 0x00 | ADC clock control register                                       |  |  |  |

| 0xB8 | IPL0           | RW | 0x00 | Interrupt priority register 0                                    |  |  |  |

| 0xB9 | ADC_RDATAH     | R  | 0x00 | ADC scan result register high 4 bits                             |  |  |  |

| 0xBA | ADC_RDATAL     | R  | 0x00 | ADC scan result register low 8 bits                              |  |  |  |

| 0xBB | ADC_CFG1       | RW | 0x00 | ADC sampling timing control register 1                           |  |  |  |

| 0xBC | ADC_CFG2       | RW | 0x02 | ADC sampling timing control register 2                           |  |  |  |

| 0xBD | UART0_BDL      | RW | 0x00 | UART0 Baudrate control registe                                   |  |  |  |

| 0xBE | UART0_CON1     | RW | 0x00 | UART0 control register 1                                         |  |  |  |

| 0xBF | UART0_CON2     | RW | 0x0C | UART0 control register 2                                         |  |  |  |

| 0xC0 | UART0_STATE    | RW | 0x00 | UART0 status flag register                                       |  |  |  |

| 0xC1 | UART0_BUF      | RW | 0xFF | UART0 data register                                              |  |  |  |

| 0xC2 | SCI_BDH        | RW | 0x00 | UART1 baudrate control register                                  |  |  |  |

| 0xC3 | SCI_BDL        | RW | 0x00 | UART1 baudrate control register                                  |  |  |  |

| 0xC4 | SCI_C1         | RW | 0x00 | UART1 control register 1                                         |  |  |  |

# BF7612CMXX-1

| 0xC5         | SCI_C2        | RW    | 0x00         | UART1 control register 2                      |

|--------------|---------------|-------|--------------|-----------------------------------------------|

| 0xC6         | SCI_C3        | RO/RW | 0x00         | UART1 control register 3                      |

| 0xC7         | SCI_S2        | RW    | 0x00         | UART1 sync segment control register           |

| 0xC8         | SCI_S1        | RO    | 0x00         | UART1 interrupt status flag register          |

| 0xC9         | SCI_D         | RW    | 0x66<br>0xFF | UART1 data register                           |

| 0xCA         | CSD_START     | RW    | 0x00         | CSD scan open register                        |

| 0xCR<br>0xCB | SNS_SCAN_CFG1 | RW    | 0x00         | Touch key scan configuration register 1       |

| 0xCC         | SNS_SCAN_CFG2 | RW    | 0x00         | Touch key scan configuration register 2       |

| 0xCD         | SNS_SCAN_CFG3 | RW    | 0x40<br>0x70 | Touch key scan configuration register 3       |

| 0xCE         | CSD_RAWDATAL  | R     | 0x70         | CSD counter, low 8-bit                        |

| 0xCE<br>0xCF | CSD_RAWDATAL  | R     | 0x00         | CSD counter, high 8-bit                       |

|              | PSW           |       |              |                                               |

| 0xD0         |               | R/RW  | 0x00         | Program status register                       |

| 0xD1         | PULL_I_SELA_L | RW    | 0x00         | CSD pull-up current source selection register |

| 0xD2         | SNS_ANA_CFG   | RW    | 0x2F         | CSD scan parameter configuration register     |

| 0xD3         | SNS_IO_SEL1   | RW    | 0x00         | SNS channel selection register 1              |

| 0xD4         | SNS_IO_SEL2   | RW    | 0x00         | SNS channel selection register 2              |

| 0xD5         | SNS_IO_SEL3   | RW    | 0x00         | SNS channel selection register 3              |

| 0xD6         | SNS_IO_SEL4   | RW    | 0x00         | SNS channel selection register 4              |

| 0xD7         | RST_STAT      | RW    | rst_state    | Reset flag register                           |

| 0xD8         | SCI_INT_CLR   | RW    | 0x00         | UART1 interrupt flag clear register           |

| 0xD9         | ADC_IO_SEL1   | RW    | 0x00         | ADC selection enable register 1               |

| 0xDA         | ADC_IO_SEL2   | RW    | 0x00         | ADC selection enable register 2               |

| 0xDB         | ADC_IO_SEL3   | RW    | 0x00         | ADC selection enable register 3               |

| 0xDC         | ADC_IO_SEL4   | RW    | 0x00         | ADC selection enable register 4               |

| 0xDD         | PU_PA         | RW    | 0x00         | PA port pull-up resistor selection register   |

| 0xDE         | PU_PB         | RW    | 0x00         | PB port pull-up resistor selection register   |

| 0xDF         | PU_PC         | RW    | 0x00         | PC port pull-up resistor selection register   |

| 0xE0         | ACC           | RW    | 0x00         | Accumulator                                   |

| 0xE1         | IRCON2        | RW    | 0x00         | Interrupt flag register 2                     |

| 0xE2         | PU_PD         | RW    | 0x00         | PD port pull-up resistor selection register   |

| 0xE3         | IICADD        | RW    | 0x00         | IIC address register                          |

| 0xE4         | IICBUF        | RW    | 0x00         | IIC transmit and receive data register        |

| 0xE5         | IICCON        | RW    | 0x10         | IIC configuration register                    |

| 0xE6         | IEN1          | RW    | 0x00         | Interrupt enable register 1                   |

| 0xE7         | IEN2          | RW    | 0x00         | Interrupt enable register 2                   |

| 0xE8         | IICSTAT       | RO/RW | 0x44         | IIC status register                           |

| 0xE9         | IICBUFFER     | RW    | 0x00         | IIC transmit and receive data buffer register |

| 0xEA         | TRISA         | RW    | 0x03         | PA port direction register                    |

| 0xEB         | TRISB         | RW    | 0xFF         | PB port direction register                    |

| <b></b> |               |    |      |                                              |

|---------|---------------|----|------|----------------------------------------------|

| 0xEC    | TRISC         | RW | 0xFF | PC port direction register                   |

| 0xED    | TRISD         | RW | 0xFF | PD port direction register                   |

| 0xEE    | COM_IO_SEL    | RW | 0x00 | COM large sink current selection register    |

| 0xEF    | ODRAIN_EN     | RW | 0x00 | PA open drain enable register                |

| 0xF0    | В             | RW | 0x00 | B register                                   |

| 0xF1    | IRCON1        | RW | 0x00 | Interrupt flag register 1                    |

| 0xF2    | PERIPH_IO_SEL | RW | 0x40 | IIC/UART0/INT function control register      |

| 0xF4    | IPL2          | RW | 0x00 | Interrupt priority register 2                |

| 0xF6    | IPL1          | RW | 0x00 | Interrupt priority register 1                |

| 0xF7    | EXT_INT_CON   | RW | 0x15 | External interrupt polarity control register |

| 0xF8    | DATAA         | RW | 0x03 | PA data register                             |

| 0xF9    | SPROG_ADDR_H  | RW | 0x00 | Address control register                     |

| 0xFA    | SPROG_ADDR_L  | RW | 0x00 | Address control register                     |

| 0xFB    | SPROG_DATA    | RW | 0x00 | Data register                                |

| 0xFC    | SPROG_CMD     | RW | 0x00 | Command register                             |

| 0xFD    | SPROG_TIM     | RW | 0x1A | Erase time control register                  |

| 0xFE    | PD_ANA        | RW | 0x1F | Module switch control register               |

| 0xFF    | SEL_LVDT_VTH  | RW | 0x00 | LVDT threshold selection register            |

SFR register summary

Note: 1. Registers whose addresses end with 8 or 0 can be bit-operated, such as register addresses 0x80, 0x88.

2. Reset value: reset value in different modes; Power-on reset: rst\_state is 0x02;

**Reset in other modes: The reset flag bit corresponding to rst\_state is 1, and other reset flags remain in their original state.**

3. RO/R: only read. RW: Read and write.

## 3.4. Secondary bus register list

The BF7612CMXX series supports expanded secondary bus registers for expanding more register functions. Just write the address of the secondary bus register to be accessed into REG\_ADDR, and then access the corresponding secondary bus register through the REG\_DATA register. It is recommended that when reading and writing secondary bus registers, EA = 0 first, and then EA = 1 after the operation is completed. Prevent other interrupts or operations from modifying the address or data of the secondary bus register.

|      | secondary bus register |       |    |       |                                                |  |  |  |

|------|------------------------|-------|----|-------|------------------------------------------------|--|--|--|

| Addr | Name                   | bit   | RW | Reset | Description                                    |  |  |  |

| 0x96 | REG_ADDR               | <5:0> | RW | 0x00  | Secondary bus address configuration register   |  |  |  |

| 0x97 | REG_DATA               | <7:0> | RW | 0x00  | x00 Secondary bus data read and write register |  |  |  |

| Addr | Name      | RW | Reset             | Description                   |

|------|-----------|----|-------------------|-------------------------------|

| 0x00 | CFG0_REG  | R  | 0xFF <sup>①</sup> | Configuration word register0  |

| 0x01 | CFG1_REG  | R  | 0xFF <sup>①</sup> | Configuration word register1  |

| 0x02 | CFG2_REG  | R  | 0xFF <sup>①</sup> | Configuration word register2  |

| 0x03 | CFG3_REG  | R  | 0xFF <sup>①</sup> | Configuration word register3  |

| 0x04 | CFG4_REG  | R  | 0xFF1             | Configuration word register4  |

| 0x05 | CFG5_REG  | R  | 0xFF <sup>①</sup> | Configuration word register5  |

| 0x06 | CFG6_REG  | R  | 0xFF <sup>①</sup> | Configuration word register6  |

| 0x07 | CFG7_REG  | R  | 0xFF <sup>①</sup> | Configuration word register7  |

| 0x08 | CFG8_REG  | R  | 0xFF1             | Configuration word register8  |

| 0x09 | CFG9_REG  | R  | 0xFF <sup>①</sup> | Configuration word register9  |

| 0x0A | CFG10_REG | R  | 0xFF <sup>①</sup> | Configuration word register10 |

| 0x0B | CFG11_REG | R  | 0xFF1             | Configuration word register11 |

| 0x0C | CFG12_REG | R  | 0xFF <sup>①</sup> | Configuration word register12 |

| 0x0D | CFG13_REG | R  | 0xFF <sup>①</sup> | Configuration word register13 |

| 0x0E | CFG14_REG | R  | 0xFF <sup>①</sup> | Configuration word register14 |

| 0x0F | CFG15_REG | R  | 0xFF <sup>①</sup> | Configuration word register15 |

| 0x10 | CFG16_REG | R  | 0xFF <sup>①</sup> | Configuration word register16 |

| 0x11 | CFG17_REG | R  | 0xFF <sup>①</sup> | Configuration word register17 |

| 0x12 | CFG18_REG | R  | 0xFF <sup>①</sup> | Configuration word register18 |

| 0x13 | CFG19_REG | R  | 0xFF <sup>①</sup> | Configuration word register19 |

| 0x14 | CFG20_REG | R  | 0xFF <sup>①</sup> | Configuration word register20 |

| 0x15 | CFG21_REG | R  | 0xFF <sup>①</sup> | Configuration word register21 |

| 0x16 | CFG22_REG | R  | 0xFF <sup>①</sup> | Configuration word register22 |

| 0x17 | CFG23_REG | R  | 0xFF <sup>①</sup> | Configuration word register23 |

| 0x18 | CFG24_REG | R  | 0xFF <sup>①</sup> | Configuration word register24 |

| 0x19 | CFG25_REG | R  | 0xFF <sup>①</sup> | Configuration word register25 |

| 0x1A | CFG30_REG  | R  | 0xFF1 | Configuration word register30                     |

|------|------------|----|-------|---------------------------------------------------|

| 0x1F | DUMMY_REG  | RW | 0x00  | RTC crystal oscillator circuit selection register |

| 0x20 | EEP_SELECT | RW | 0x00  | EEP NVR/main block selection register             |

Note:

- 1. '①': The reset value is the default value after power-on reset, and the value after the global reset is completed is the factory calibration value;

- 2. 'R': Read only; 'RW': Read and write.

## 4. Register Summary

## 4.1. SFR Register details

| DATAB(80H)PB port data register |

|---------------------------------|

|---------------------------------|

| Bit number  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol      | PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 |

| R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Bit number | Bit symbol | Description                                                    |

|------------|------------|----------------------------------------------------------------|

|            |            | The output level of the PB group can be configured as the      |

| 7~0        |            | GPIO port. The read value is the level state of the current IO |

|            |            | port or the configured output value.                           |

SP(81H) Stack pointer register

| DI (OIII) Diack                           | SI (0111) Stack pointer register           |                 |            |   |        |   |   |   |  |

|-------------------------------------------|--------------------------------------------|-----------------|------------|---|--------|---|---|---|--|

| Bit number                                | 7                                          | 6               | 5          | 4 | 3      | 2 | 1 | 0 |  |

| Symbol                                    |                                            |                 |            | S | P[7:0] |   |   |   |  |

| R/W                                       |                                            |                 |            | ] | R/W    |   |   |   |  |

| Reset value                               |                                            |                 |            |   | 7      |   |   |   |  |

| DPL(82H) Data pointer register0 low 8-bit |                                            |                 |            |   |        |   |   |   |  |

| Bit number                                | 7                                          | 6               | 5          | 4 | 3      | 2 | 1 | 0 |  |

| Symbol                                    | DPL[7:0]                                   |                 |            |   |        |   |   |   |  |

| R/W                                       | R/W                                        |                 |            |   |        |   |   |   |  |

| Reset value                               | 0                                          |                 |            |   |        |   |   |   |  |

| DPH(83H) Data                             | DPH(83H) Data pointer register0 high 8-bit |                 |            |   |        |   |   |   |  |

| Bit number                                | 7                                          | 7 6 5 4 3 2 1 0 |            |   |        |   |   |   |  |

| Symbol                                    |                                            | DPH[7:0]        |            |   |        |   |   |   |  |

| R/W                                       | R/W                                        |                 |            |   |        |   |   |   |  |

| Reset value                               | 0                                          |                 |            |   |        |   |   |   |  |

| SYS_CLK_CFC                               | G(84H) Cl                                  | ock contro      | l register |   |        |   |   |   |  |

| Bit number                                | 7                                          | 6               | 5          | 4 | 3      | 2 | 1 | 0 |  |

| Symbol      | - | - | - | - | - | - | PLL_CLK_SEL[1:0] |  |  |

|-------------|---|---|---|---|---|---|------------------|--|--|

| R/W         | - | - | - | - | - | - | R/W              |  |  |

| Reset value | - | - | - | - | - | - | 0 1              |  |  |

| Bit number  | В             | it symł | ool                                         | Description                          |          |         |              |                 |  |  |  |

|-------------|---------------|---------|---------------------------------------------|--------------------------------------|----------|---------|--------------|-----------------|--|--|--|

| 7~2         |               |         |                                             | Reserved                             |          |         |              |                 |  |  |  |

| 1~0         | PLL           | _CLK    | _SEL                                        | PLL clock divided selection register |          |         |              |                 |  |  |  |

|             |               |         | 00: 12Mhz; 01: 6Mhz; 10: 4Mhz; 11: Reserved |                                      |          |         |              |                 |  |  |  |

| INT_PE_STAT | <u>Г(85H)</u> | WDT/    | Timer <sup>2</sup>                          | 2 interr                             | upt stat | tus reg | ister        |                 |  |  |  |

| Bit number  | 7             | 6       | 5                                           | 4                                    | 3        | 2       | 1            | 0               |  |  |  |

| Symbol      | Ι             | -       | -                                           | -                                    | -        | -       | INT_WDT_STAT | INT_TIMER2_STAT |  |  |  |

| R/W         | -             | -       | -                                           | -                                    | R/W R/W  |         |              |                 |  |  |  |

| Reset value | -             | -       | -                                           | -                                    | -        | -       | 0            | 0               |  |  |  |

| Bit number | Bit symbol      | Description                                            |

|------------|-----------------|--------------------------------------------------------|

|            |                 | WDT interrupt status, set 0, write WDT_CTRL can set 0. |

| 1          | INT_WDT_STAT    | 1: interrupt effective                                 |

|            |                 | 0: invalid interrupt                                   |

|            |                 | TIMER2 interrupt status, set 0, write TIMER2_CFG can   |

| 0          | INT_TIMER2_STAT | set 0.                                                 |

| 0          |                 | 1: interrupt effective                                 |

|            |                 | 0: invalid interrupt                                   |

### INT\_POBO\_STAT (86H) LVDT boost/LVDT buck interrupt status register

| Bit number  | 7 | 6 | 5 | 4 | 3 | 2 | 1           | 0           |

|-------------|---|---|---|---|---|---|-------------|-------------|

| Symbol      | - | - | - | - | I | - | INT_PO_STAT | INT_BO_STAT |

| R/W         | - | - | - | - | - | - | R/W         | R/W         |

| Reset value | - | - | - | - | I | - | 0           | 0           |

| Bit number | Bit symbol  | Description                   |

|------------|-------------|-------------------------------|

|            |             | Lvdt boost interrupt status   |

| 1          | INT_PO_STAT | 1: boost interrupt is valid   |

|            |             | 0: boost interrupt is invaild |

|            |             | Lvdt buck interrupt state     |

| 0          | INT_BO_STAT | 1: buck interrupt is valid    |

|            |             | 0: buck interrupt is invalid  |

### PCON (87H) Idle mode selection register

| Bit number  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-------------|---|---|---|---|---|---|---|-------|

| Symbol      | - | - | - | - | - | - | - | IM_EN |

| R/W         | - | - | - | - | - | - | - | R/W   |

| Reset value | - | _ | _ | - | _ | _ | - | 0     |

| Bit number   | Bit symbol           | Description                                                                                                           |

|--------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0            | IM_EN                | <ul><li>idle mode control</li><li>1: idle mode;</li><li>0: normal mode, automatically cleared after wake-up</li></ul> |

| TCON(88H) Ti | mer control register |                                                                                                                       |

| Bit number  | 7   | 6   | 5   | 4   | 3   | 2 | 1   | 0 |

|-------------|-----|-----|-----|-----|-----|---|-----|---|

| Symbol      | TF1 | TR1 | TF0 | TR0 | IE1 | - | IE0 | - |

| R/W         | R/W | R/W | R/W | R/W | R/W | - | R/W | - |

| Reset value | 0   | 0   | 0   | 0   | 0   | - | 0   | _ |

| Bit number | Bit symbol | Description                                                                                       |

|------------|------------|---------------------------------------------------------------------------------------------------|

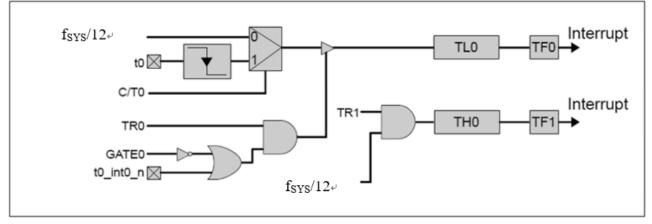

| 7          | TF1        | Timer1 overflow flag. Set to 1 when Timer1 overflows, or<br>Timer0's TH0 overflows in mode three. |

| 6          | TR1        | Timer1 start enable, When set to 1, start Timer1, or start<br>Timer0 mode three TH0 counte.       |

| 5          | TF0        | Timer0 overflow flag, the hardware set 1 when Timer0 overflows.                                   |

| 4          | TR0        | Timer0 start enable, when set to 1, start Timer0 count.                                           |

| 3          | IE1        | External interrupt 1. The hardware set 1, the software is cleared.                                |

| 2          |            | Reserved                                                                                          |

| 1          | IE0        | External interrupt 0. The hardware set 1, the software is cleared                                 |

| 0          |            | Reserved                                                                                          |

TMOD(89H) Timer mode register

| Bit number  | 7 | 6 | 5       | 4 | 3 | 2 | 1       | 0 |

|-------------|---|---|---------|---|---|---|---------|---|

| Symbol      | - | - | M1[1:0] |   | - | - | M0[1:0] |   |

| R/W         | - | - | R/W     |   | - | - | R/      | W |

| Reset value | - | _ | 0       | 0 | - | - | 0       | 0 |

| Bit number | Bit symbol | Description                                                                                                                                                                        |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~6        |            | Reserved                                                                                                                                                                           |

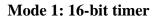

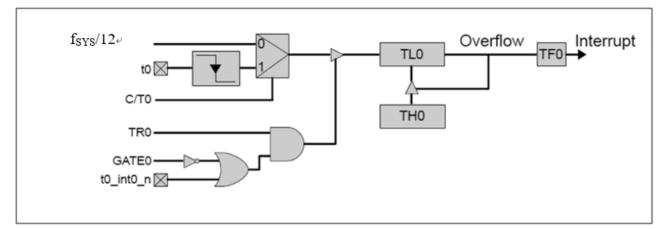

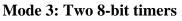

| 5~4        | M1[1:0]    | M1-Timer1: Bit 1, M1-Timer1: Bit 0.<br>00=mode0 – 13 bit Timer<br>01=mode1 – 16 bit Timer<br>10=mode2 – 8-bit timer with automatic reload initial value<br>11=mode3 – 2*8bit Timer |

| 3~2        |            | Reserved                                                                                                                                                                           |

| 1~0        | M0[1:0]    | M0-Timer0: Bit 1, M0-Timer0: Bit 0.                                                                                                                                                |

|               |             |                                                              | 00=mode | 0 – 13 bit 7   | Timer |   |   |          |  |  |

|---------------|-------------|--------------------------------------------------------------|---------|----------------|-------|---|---|----------|--|--|

|               |             |                                                              |         | 1 - 16 bit $1$ |       |   |   |          |  |  |

|               |             | 10 = mode2 - 8 bit timer with automatic reload initial value |         |                |       |   |   |          |  |  |

|               |             |                                                              |         | 3 - 2*8bit     |       |   |   | ii value |  |  |

| TL0(8AH) Time | er 0 counte | r low 8-bit                                                  |         | 5 2 001        | Timer |   |   |          |  |  |

| Bit number    | 7           | 6                                                            | 5       | 4              | 3     | 2 | 1 | 0        |  |  |

| Symbol        |             |                                                              |         | TL0            | [7:0] |   | • |          |  |  |

| R/W           |             |                                                              |         | <b>R</b> /     | W     |   |   |          |  |  |

| Reset value   |             |                                                              |         | 0              | )     |   |   |          |  |  |

| TL1(8BH) Time | er 1 counte | r low 8-bit                                                  |         |                |       |   |   |          |  |  |

| Bit number    | 7           | 6                                                            | 5       | 4              | 3     | 2 | 1 | 0        |  |  |

| Symbol        |             |                                                              |         | TL1[           | [7:0] |   |   |          |  |  |

| R/W           |             |                                                              |         | <b>R</b> /     | W     |   |   |          |  |  |

| Reset value   |             |                                                              |         | 0              | )     |   |   |          |  |  |

| TH0(8CH) Time | er 0 counte | r high 8-bi                                                  | t       |                |       |   | • |          |  |  |

| Bit number    | 7           | 6                                                            | 5       | 4              | 3     | 2 | 1 | 0        |  |  |

| Symbol        |             |                                                              |         | TH0            | [7:0] |   |   |          |  |  |

| R/W           |             |                                                              |         | R/             | W     |   |   |          |  |  |

| Reset value   |             |                                                              |         | 0              | )     |   |   |          |  |  |

| TH1(8DH) Time | er 1 counte | r high 8-bi                                                  | t       |                |       |   |   |          |  |  |

| Bit number    | 7           | 6                                                            | 5       | 4              | 3     | 2 | 1 | 0        |  |  |

| Symbol        |             |                                                              |         | TH1            | [7:0] |   |   |          |  |  |

| R/W           |             |                                                              |         | R/             | W     |   |   |          |  |  |

| Reset value   |             |                                                              |         | 0              | )     |   |   |          |  |  |

| SOFT_RST(8EF  |             | et register                                                  |         |                |       |   |   |          |  |  |

| Bit number    | 7           | 6                                                            | 5       | 4              | 3     | 2 | 1 | 0        |  |  |

| Symbol        |             |                                                              |         | -              |       |   |   |          |  |  |

| R/W           |             | R/W                                                          |         |                |       |   |   |          |  |  |

| Reset value   |             |                                                              |         | 0              | )     |   |   |          |  |  |

|               |             |                                                              |         |                |       |   |   |          |  |  |

| Bit number | Bit symbol | Description                                               |

|------------|------------|-----------------------------------------------------------|

| 7~0        |            | Software reset register. Software reset is only generated |

|            |            | when the register value is 0x55.                          |

## DATAC(90H) PC port data register

| Bit number  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol      | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

| R/W         |     | R/W |     |     |     |     |     |     |

| Reset value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Bit number | Bit symbol | Description                                                    |

|------------|------------|----------------------------------------------------------------|

|            |            | PC data register. The output level of the PC group can be      |

| 7~0        |            | configured as the GPIO port. The read value is the level state |

|            |            | of the current IO port or the configured output value.         |

WDT\_CTRL(91H) WDT timing overflow control register

|             | / | <u> </u> |   |   |   |    |         |     |

|-------------|---|----------|---|---|---|----|---------|-----|

| Bit number  | 7 | 6        | 5 | 4 | 3 | 2  | 1       | 0   |

| Symbol      | - | -        | - | - | - | WD | T_TIME_ | SEL |

| R/W         | - | -        | - | - | - |    | R/W     |     |

| Reset value | - | -        | - | - | - | 0  | 0       | 0   |

| Bit number | Bit symbol   | Description                                               |

|------------|--------------|-----------------------------------------------------------|

|            | WDT_TIME_SEL | WDT overflow timer register. Timing length is as follows: |

| 2~0        |              | 0x00: 18ms; 0x01: 36ms; 0x02: 72ms; 0x03: 144ms;          |

|            |              | 0x04: 288ms; 0x05: 576ms; 0x06: 1152ms; 0x07: 2304ms;     |

WDT\_EN(92H) WDT timing enable register

| Bit number  | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|--------|---|---|---|---|---|---|

| Symbol      |   | WDT_EN |   |   |   |   |   |   |

| R/W         |   | R/W    |   |   |   |   |   |   |

| Reset value | 0 |        |   |   |   |   |   |   |

| Bit number | Bit symbol | Description                                                                                       |

|------------|------------|---------------------------------------------------------------------------------------------------|

| 7~0        | WDT_EN     | WDT timing enable configuration register. WDT is turned off when the configuration value is 0x55. |

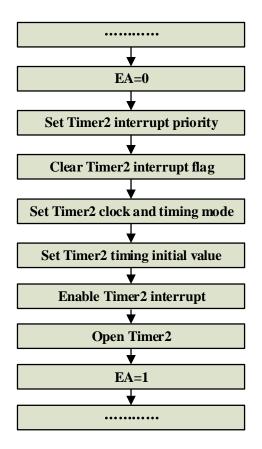

### TIMER2\_CFG (93H) TIMER2 configuration register

| Bit number  | 7 | 6 | 5 | 4 | 3              | 2              | 1          | 0         |

|-------------|---|---|---|---|----------------|----------------|------------|-----------|

| Symbol      | - | I | I | I | TIMER2_CNT_MOD | TIMER2_CLK_SEL | TIMER2_RLD | TIMER2_EN |

| R/W         | - | 1 | 1 | I | R/W            | R/W            | R/W        | R/W       |

| Reset value | - | I | I | I | 0              | 0              | 0          | 0         |

| Bit number | Bit symbol     | Description                               |

|------------|----------------|-------------------------------------------|

|            |                | TIMER2 count step mode selection register |

| 3          | TIMER2_CNT_MOD | 1: count step is 65536 clock.             |

|            |                | 0: count step is 1 clock.                 |

|            |                | TIMER2 clock selection register           |

| 2          | TIMER2_CLK_SEL | 1: select XTAL                            |

|            |                | 0: select LIRC                            |

|            |                | TIMER2 reload enable control register     |

| 1          | TIMER2_RLD     | 1: automatic reload mode                  |

|            |                | 0: manual reload mode                     |

| 0          | TIMER2_EN      | TIMER2 count enable register              |

|  | 1: turn on timing; 0: stop timing;                          |

|--|-------------------------------------------------------------|

|  | In manual reload mode, the hardware automatically           |

|  | clears this register after timing is completed, stop count. |

|  | In manual reload mode, will maintain the enable register    |

|  | after the count is completed. Automatically re-counting     |

|  | from 0, no matter which mode, configuring this register     |

|  | to 1 during counting will start counting from 0.            |

TIMER2\_SET\_H(94H) TIMER2 count value configuration register, high 8 bits

|             |   |     |   |   | <u> </u> | 0 |   |   |  |

|-------------|---|-----|---|---|----------|---|---|---|--|

| Bit number  | 7 | 6   | 5 | 4 | 3        | 2 | 1 | 0 |  |

| Symbol      |   | _   |   |   |          |   |   |   |  |

| R/W         |   | R/W |   |   |          |   |   |   |  |

| Reset value |   | 0   |   |   |          |   |   |   |  |

| Bit number                                                              | Bit symbol | Description                                                                                                 |  |  |  |

|-------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 7~0                                                                     |            | TIMER2 count configuration register, high 8 bit,<br>Configuring this register during the scan will recount. |  |  |  |

| TIMER2_SET_L(95H) TIMER2 count value configuration register, low 8 bits |            |                                                                                                             |  |  |  |

| The RZ_SET_E() STITUTERZ Count value configuration register, fow 8 ons |   |                 |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------|---|-----------------|--|--|--|--|--|--|--|--|--|

| Bit number                                                             | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

| Symbol                                                                 |   | -               |  |  |  |  |  |  |  |  |  |

| R/W                                                                    |   | R/W             |  |  |  |  |  |  |  |  |  |

| Reset value                                                            |   | 0               |  |  |  |  |  |  |  |  |  |

| Bit number | Bit symbol | Description                                                                                             |

|------------|------------|---------------------------------------------------------------------------------------------------------|

| 7~0        |            | TIMER2 count configuration register, low 8 bit, Configuring this register during the scan will recount. |

### REG\_ADDR (96H) Second address bus register

| Bit number  | 7 | 6 | 5 | 4 | 3        | 2 | 1 | 0 |  |  |  |

|-------------|---|---|---|---|----------|---|---|---|--|--|--|

| Symbol      | - | - |   |   | REG_ADDR |   |   |   |  |  |  |

| R/W         | - | - |   |   | R/       | W |   |   |  |  |  |

| Reset value | - | - | 0 | 0 | 0        | 0 | 0 | 0 |  |  |  |

| Bit number | Bit symbol | Description                                                                                                                                                                                                                                                                                                                       |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5~0        | REG_ADDR   | Secondary bus address configuration register. When<br>operating the secondary bus, it is recommended to read and<br>write the secondary bus register, $EA = 0$ first, $EA = 1$ after<br>the operation is completed, to prevent other interruptions or<br>operations from modifying the secondary bus register<br>address or data. |

| REG_DATA (9 | (H) Secon | d bus data | read and w | vrite registe | er |   |   |   |

|-------------|-----------|------------|------------|---------------|----|---|---|---|

| Bit number  | 7         | 6          | 5          | 4             | 3  | 2 | 1 | 0 |

| Symbol      | REG_DATA |

|-------------|----------|

| R/W         | R/W      |

| Reset value | 0        |

| Bit number | Bit symbol | Description                                                                                                                                                                                                                                                                        |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~0        | REG_DATA   | Secondary bus read and write registers. It is recommended to<br>read and write the secondary bus register, EA = 0 first, EA =<br>1 after the operation is completed, to prevent other<br>interruptions or operations from modifying the secondary<br>bus register address or data. |

DATAD(98H) PD port data register

| Bit number  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol      | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 |

| R/W         |     | R/W |     |     |     |     |     |     |

| Reset value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Bit number | Bit symbol | Description                                                    |

|------------|------------|----------------------------------------------------------------|

|            |            | PD data register. The output level of the PD group can be      |

| 7~0        |            | configured as the GPIO port. The read value is the level state |

|            |            | of the current IO port or the configured output value.         |

PWM1\_L\_L (99H) PWM1 low level control register(low 8-bit)

| Bit number  | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

|-------------|---|-----------------|--|--|--|--|--|--|--|--|--|

| Symbol      |   | _               |  |  |  |  |  |  |  |  |  |

| R/W         |   | R/W             |  |  |  |  |  |  |  |  |  |

| Reset value |   | 0               |  |  |  |  |  |  |  |  |  |

#### PWM1\_L\_H (9AH) PWM1 PWM1 low level control register(high 8-bit)

| Bit number  | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------------|---|---|---|----|---|---|---|---|--|--|

| Symbol      |   | _ |   |    |   |   |   |   |  |  |

| R/W         |   |   |   | R/ | W |   |   |   |  |  |

| Reset value |   | 0 |   |    |   |   |   |   |  |  |

PWM1\_H\_L (9BH) PWM1 high level control register(low 8-bit)

| Bit number  | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------|---|-----|---|---|---|---|---|---|--|--|

| Symbol      |   | -   |   |   |   |   |   |   |  |  |

| R/W         |   | R/W |   |   |   |   |   |   |  |  |

| Reset value |   |     |   | ( | ) |   |   |   |  |  |

#### PWM1\_H\_H (9CH) PWM1 high level control register(high 8-bit)

| Bit number  | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|-------------|---|---|---|----|---|---|---|---|

| Symbol      |   |   |   | -  | - |   |   |   |

| R/W         |   |   |   | R/ | W |   |   |   |

| Reset value |   |   |   | (  | ) |   |   |   |

| PWM2_L_L (91  | JH) PWM | 2 low leve                                    | l control re  | gister(low  | 8-D1t)   |   |   |   |  |

|---------------|---------|-----------------------------------------------|---------------|-------------|----------|---|---|---|--|

| Bit number    | 7       | 6                                             | 5             | 4           | 3        | 2 | 1 | 0 |  |

| Symbol        |         |                                               |               |             |          |   |   |   |  |

| R/W           |         |                                               |               | R/          | W        |   |   |   |  |

| Reset value   |         |                                               |               | (           | )        |   |   |   |  |